Chapter 1. Technical description

11

This is new and the “closest” to the processor, and is used to store

micro-operations. These are decoded executable machine instructions. It

serves these to the processor at rated speed. This additional level of cache

saves decode time on cache hits.

Level 2 cache, 256 KB

This is equivalent to L1 cache on the Pentium® III Xeon.

Level 3 cache 3–6 MB

This is equivalent to L2 cache on the Pentium III Xeon or the L3 cache on the

Pentium Xeon MP processor. Unlike the design of the original Itanium

processor, this L3 cache is now on the processor die, greatly improving

performance, up to 2 times greater than that of the original Itanium.

The x455 also implements a Level 4 cache as described in “IBM XceL4

Accelerator Cache” on page 12.

Intel has also introduced a number of features associated with its Itanium

micro-architecture. These are available in the x455, including:

400 MHz frontside bus

The Pentium III Xeon processor had a 100 MHz frontside bus that equated to

a burst throughput of 800 MBps. With protocols such as TCP/IP, this had been

shown to be a bottleneck in high-throughput situations. The Itanium 2

processor improves on this by using a single 200 MHz clock but using both

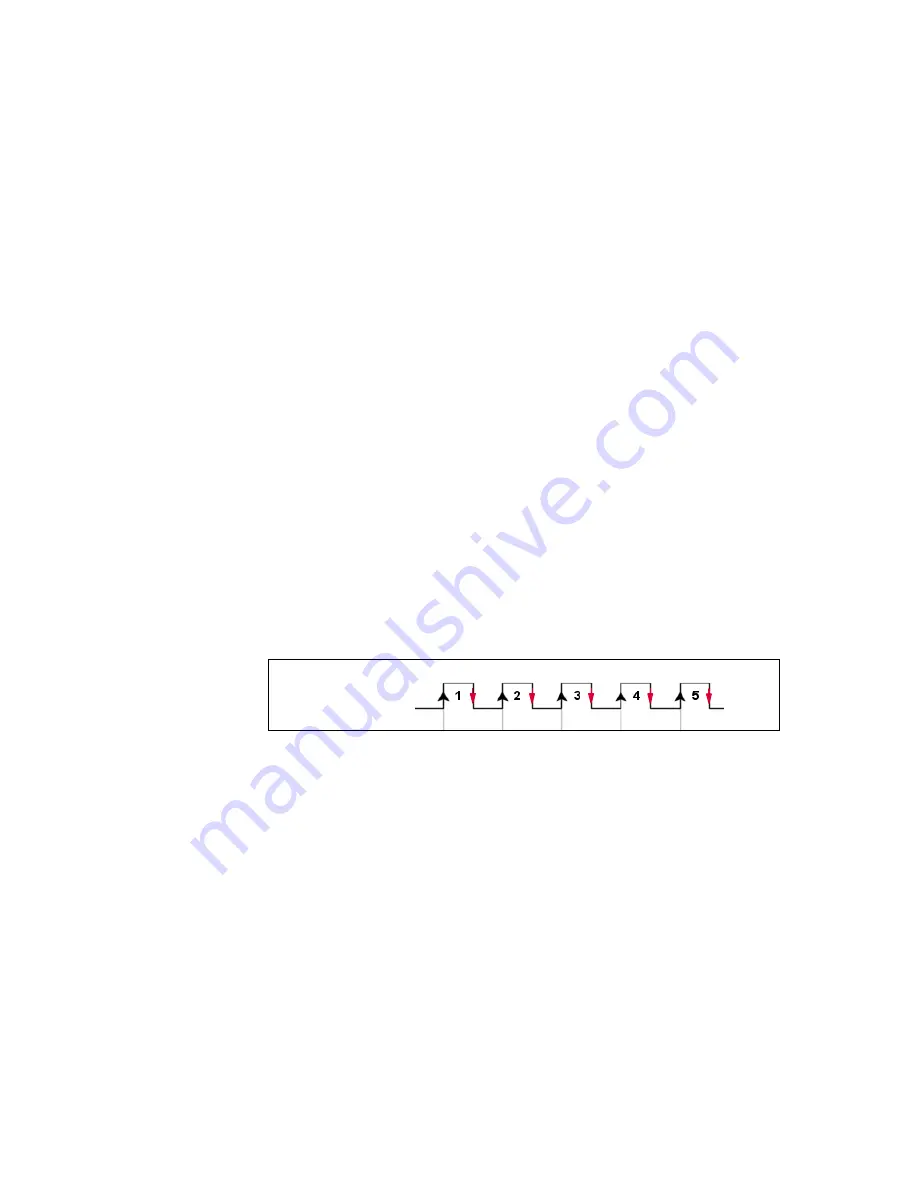

edges of each clock cycle to transmit data. This is shown in Figure 1-6.

Figure 1-6 Dual-pumped frontside bus

This increases the performance of the frontside bus. The end result is an

effective burst throughput of 6.4 GBps (128-bit wide data path running at 400

MHz), which can have a substantial impact, especially on TCP/IP-based LAN

traffic. This is opposed to the Itanium processor, which had a burst throughput

of only 2.1 GBps (64-bit wide data path running at 266 MHz).

Explicitly Parallel Instruction Computing (EPIC)

EPIC technology, developed by Intel and HP, leads to more efficient, faster

processors because it eliminates numerous processing inefficiencies in

current processors and attacks the perennial data bottleneck problems by

increasing parallelism, rather than simply boosting the raw “clock” speed of

the processor.

200 MHz clock

Summary of Contents for 88553RX

Page 2: ......

Page 214: ...200 IBM Eserver xSeries 455 Planning and Installation Guide Figure 5 14 Connect to the x455...

Page 228: ...214 IBM Eserver xSeries 455 Planning and Installation Guide...

Page 229: ...IBM Eserver xSeries 455 Planning and Installation Guide...

Page 230: ......

Page 231: ......