Preliminary

www.ti.com

Architecture

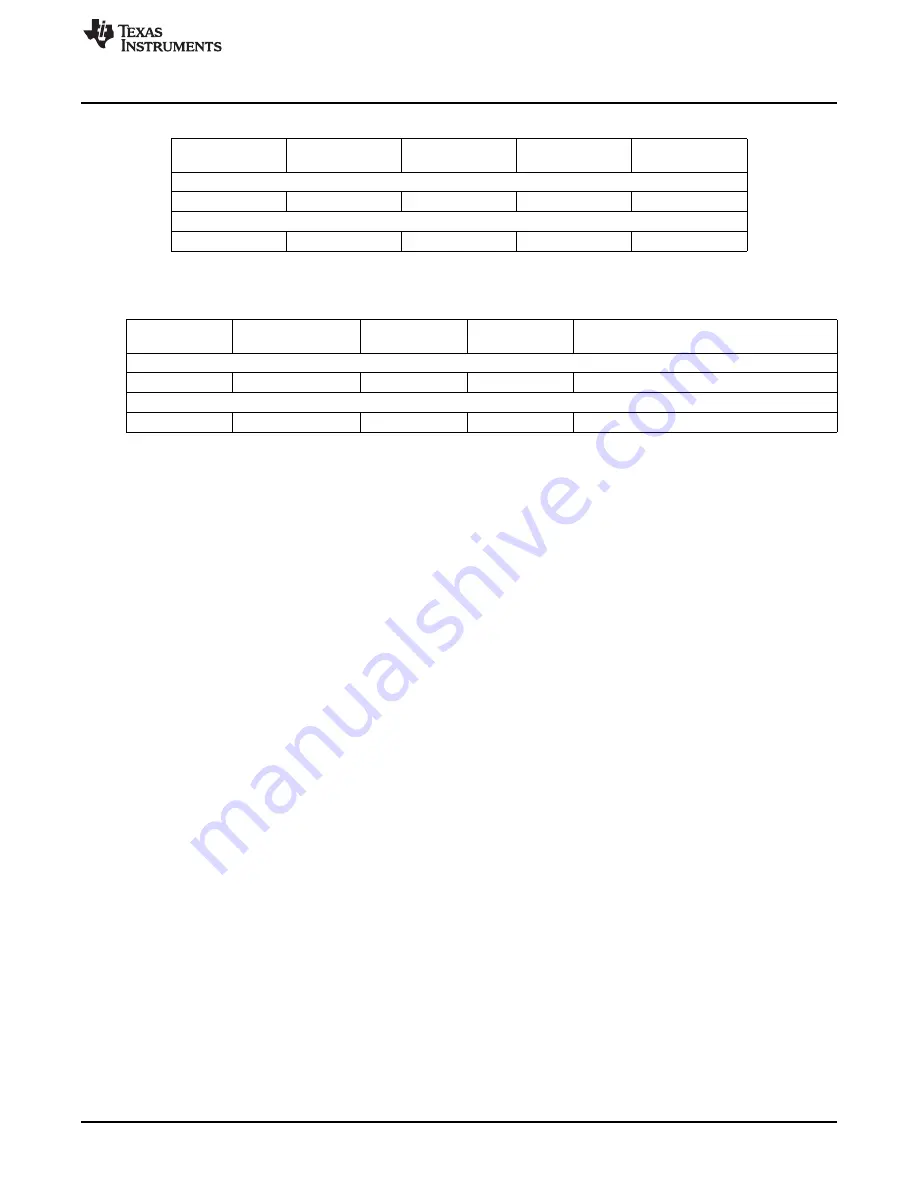

Table 5-4. GPMC Clocks and Resets

Destination Signal

Source Signal

Module Instance

Source

Description

Name

Name

Clocks

GPMC

GPMC_FCLK

prcm_GPMC_CLK

PRCM

Functional clock

Resets

GPMC

GPMC_RST

ALW_DOM_RST

PRCM

GPMC reset

Table 5-5. GPMC Hardware Requests

Destination

Module Instance

Source Signal Name

Destination

Description

Signal Name

Interrupt Requests

GPMC

GPMC_IRQ

A_IRQ_100

Cortex-A8

GPMC interrupt to Cortex-A8 MPU subsystem

DMA Requests

GPMC

GPMC_DMA_REQ

e_DMA_52

eDMA

GPMC request from Prefetch Engine to eDMA

5.2.4 GPMC Functional Description

The GPMC basic programming model offers maximum flexibility to support various access protocols for

each of the eight configurable chip-selects. Use optimal chip-select settings, based on the

characteristics of the external device:

•

Different protocols can be selected to support generic asynchronous or synchronous random-access

devices (NOR flash, SRAM) or to support specific NAND devices.

•

The address and the data bus can be multiplexed on the same external bus.

•

Read and write access can be independently defined as asynchronous or synchronous.

•

System requests (byte, 16-bit word, burst) are performed through single or multiple accesses.

External access profiles (single, multiple with optimized burst length, native- or emulated-wrap) are

based on external device characteristics (supported protocol, bus width, data buffer size,

native-wrap support).

•

System burst read or write requests are synchronous-burst (multiple-read or multiple-write). When

neither burst nor page mode is supported by external memory or ASIC devices, system burst read

or write requests are translated to successive single synchronous or asynchronous accesses (single

reads or single writes). 8-bit wide devices are supported only in single synchronous or single

asynchronous read or write mode.

•

To simulate a programmable internal-wait state, an external wait pin can be monitored to

dynamically control external access at the beginning (initial access time) of and during a burst

access.

Each control signal is controlled independently for each chip-select. The internal functional clock of the

GPMC (GPMC_FCLK) is used as a time reference to specify the following:

•

Read- and write-access duration

•

Most GPMC external interface control-signal assertion and deassertion times

•

Data-capture time during read access

•

External wait-pin monitoring time

•

Duration of idle time between accesses, when required

559

SPRUGX9 – 15 April 2011

General-Purpose Memory Controller (GPMC)

© 2011, Texas Instruments Incorporated