Functions

6-135

7SA522 Manual

C53000-G1176-C119-2

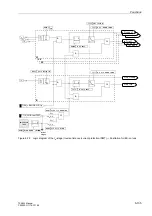

Figure 6-78

Logic diagram of the I

p

–stage (inverse time overcurrent protection IDMT) — illustration for IEC–curves

≥

1

Yes

No

,,S627)

Yes

No

further

stages

3I

0P

&

&

≥

1

E

I

E

2652

7,S7LPH'LDO

T

0

t

I

I

P

&

&

≥

1

L1

2642

7,S7LPH'LDO

7,S$GG

T

0

2660

,(&&XUYH

t

I

I

L3

I

L2

I

L1

L2

L3

,3

2656

7,S$GG

,S3,&.83

switch onto

fault

T

0

627)7LPH'(/$<

,,S7HOH%,

Ip Pickup L3

Ip Pickup L2

Ip Trip L3

Ip Trip L2

Ip Pickup L1

Ip Trip L1

3I0p Trip

3I0p Pickup

7106 >BLOCK O/C Ip

7110 >O/C InstTRIP

Summary of Contents for siprotec 7SA522

Page 20: ...7SA522 Manual C53000 G1176 C119 2 ...

Page 64: ...7SA522 Manual C53000 G1176 C119 2 ...

Page 89: ...SIPROTEC 4 Devices 4 25 7SA522 Manual C53000 G1176 C119 2 Figure 4 20 CFC Logic example ...

Page 408: ...7SA522 Manual C53000 G1176 C119 2 ...

Page 456: ...7SA522 Manual C53000 G1176 C119 2 ...

Page 516: ...7SA522 Manual C53000 G1176 C119 2 ...

Page 620: ...Appendix B 48 ...