MMUART Peripherals

UG0331 User Guide Revision 15.0

503

13.4.18 Transmitter Time Guard Register (TTG)

13.4.19 Receiver Timeout Register (RTO)

13.4.20 Address Register (ADR)

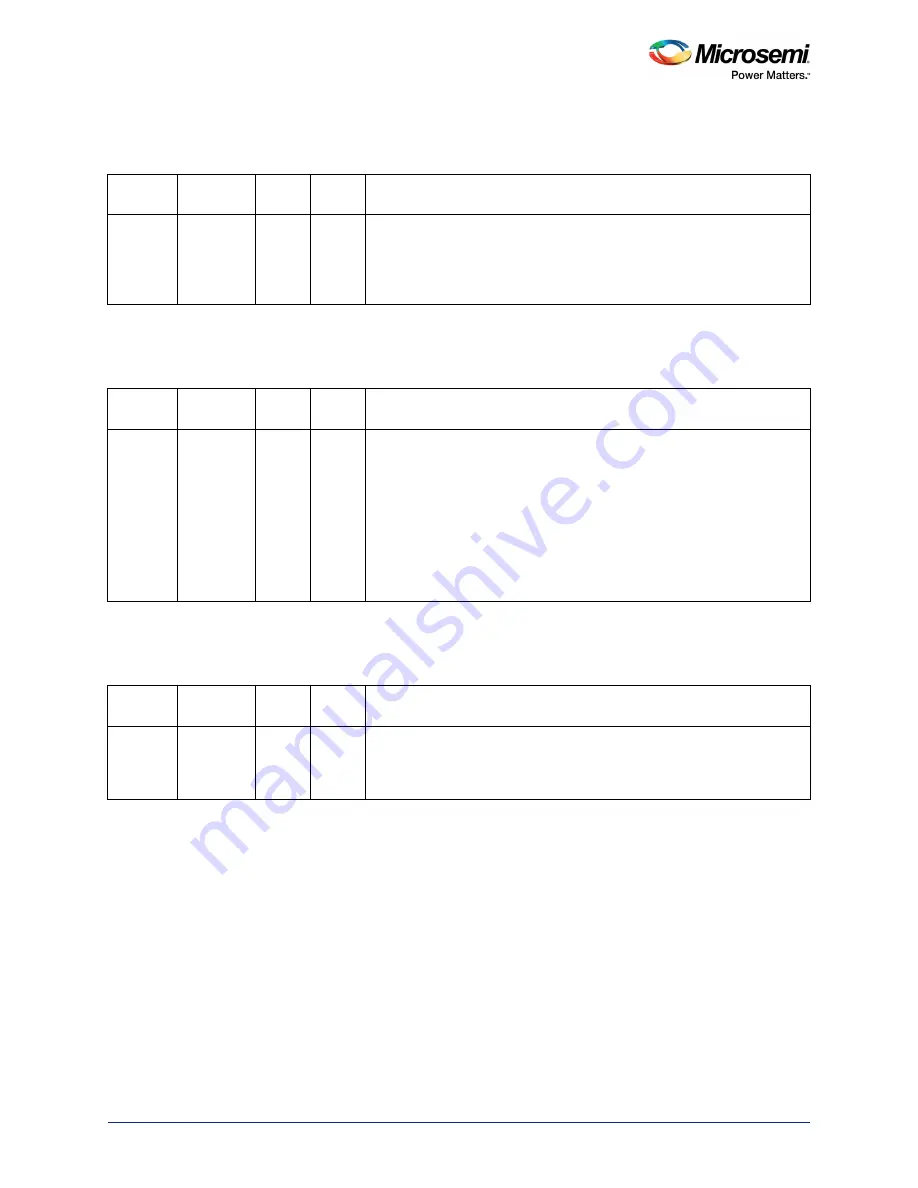

Table 489 •

TTG

Bit

Number

Name

R/W

Reset

Value

Description

[7:0]

TTG

R/W

0

If the transmitter time guard is enabled from the multi-mode control

register 0 (

), the transmitter time guard value determines the amount

of system clock cycles to wait between transmissions. The time guard

equation is based on the baud rate bit time (Tbit) value as follows:

Tx Time Guard Value = TTG x Bit Time (Tbit)

Table 490 •

RTO

Bit

Number

Name

R/W

Reset

Value

Description

[7:0]

RTO

R/W

0

Writing to the RTO register sets the counter value and enables, if the

ERTO bit in the

is enabled. You can configure the timeout value by

writing into this register. The RTO counts when the Rx block input state is

idle; is reset when a start condition occurs, and restarts counting upon

returning to the idle state. When the RTO value is reached, the RTOII

interrupt is set. Re-writing the RTO register clears the interrupt and sets

the counter.

The receiver timeout value equation is based on the baud rate bit time

(Tbit) as follows:

Rx Timeout Value = 4 x RTO x Bit Time (Tbit)

Table 491 •

ADR

Bit

Number

Name

R/W

Reset

Value

Description

[7:0]

ADR

R/W

0

The address register is used in 9-bit Address Flag mode. When an

address flag is received on the 9

th

bit, and EAFM is set in

, the

incoming data is checked against the address register. If a match occurs,

the Rx FIFO is enabled.