MMUART Peripherals

UG0331 User Guide Revision 15.0

485

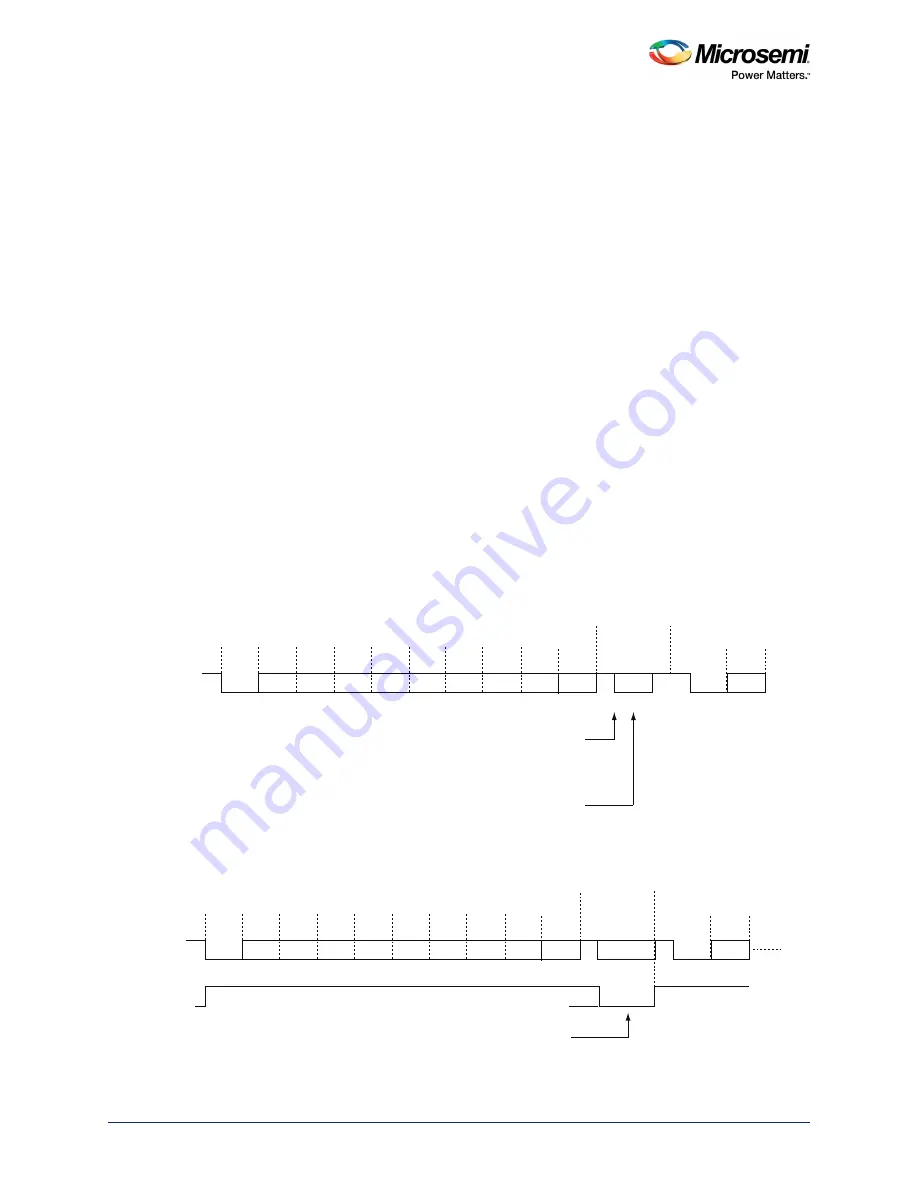

13.2.4.10 ISO7816-3 Modes

The ISO7816 is an international standard related to electronic identification cards. The ISO7816-3

utilizes a half-duplex, bi-directional bus for data transfers. The MMUART provides the clock to the smart

card IC and is therefore considered the master in the system and smart card is the slave. MMUART

supports T0/T1 addressing modes. Protocol T=0 is the asynchronous half-duplex character transmission

protocol whereas T=1 is the asynchronous half-duplex block transmission protocol. The T0 protocol is a

byte-oriented protocol where a character is transmitted across the channel between the reader

(MMUART) and the card.

In addition, error handling is performed on each byte by looking at the parity bit. If the actual parity bit

does not correspond to the parity of the transmitted data, then an error must have occurred. In the T0

protocol, the receiving side signals that it requires the byte to be retransmitted in case of detecting a

parity error. This is done by holding the I/O line low (the I/O line is set High preceding the transfer of a

byte). When the transmitting side detects this, it resends the byte that was not received correctly. The

transmitter output enable is enabled during the transmission of the start bit and data byte and is disabled

during the stop bit.

For T = 0 protocol, the format of the data is composed of 1 start bit, 8 data bits, 1 parity bit, and 1 guard

time, which is composed of 2-bit times. The transmitter shifts all the data out except during the guard

time. The guard time is used by the receiver to NACK the transmission. When the EERR bit in MM2 is

set, the receiver will force an error signal to transmit out, if an incoming parity error is detected. In this

case the I/O signal is held Low for one Tbit time starting from 10.5. When transmitting, the 11th Tbit in the

ACK/NACK window is sampled from the Rx input, generating an interrupt if NACK (NACKI interrupt can

be enabled by modifying

register) is detected. The following figures show the timing diagrams for I/O

signals, the Transmit mode output enable and the Receive mode output enable when EERR is set to 1.

Note:

The Tx Transmit mode output enable (TE) is disabled during a parity error to prevent any wrong data

from being transmitted.

Similarly, the Rx mode output enable (TE) is enabled during parity error to allow the retransmission of

data.

Figure 195 •

Single Wire Error Signal Timing when EERR=1

Figure 196 •

Transmit Mode TE Output Enable Timing when EERR=1

I/O Data

Signal

2 Stops Bits

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

ACK/

NACK

2

1

0

12

11

10.5

10

9

8

7

6

5

4

3

2

1

0

If there is an input received

parity error, the output is

held low for 1.0 Tbits

starting at 10.5

The output transmitter

samples the received signal

at the 11th Tbit for ACK/

NACK and sets an interrupt

if NACK (NACKI)

Parity

2 Stops Bits

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

Tbit

ACK/NACK

2

1

0

12

11

10.5

10

9

8

7

6

5

4

3

2

1

0

Tx Transmit Enable Output

disabled during ACK/NACK

window

Parity

Tx Data

TE