FRCTL_A Registers

308

SLAU367P – October 2012 – Revised April 2020

Copyright © 2012–2020, Texas Instruments Incorporated

FRAM Controller A (FRCTL_A)

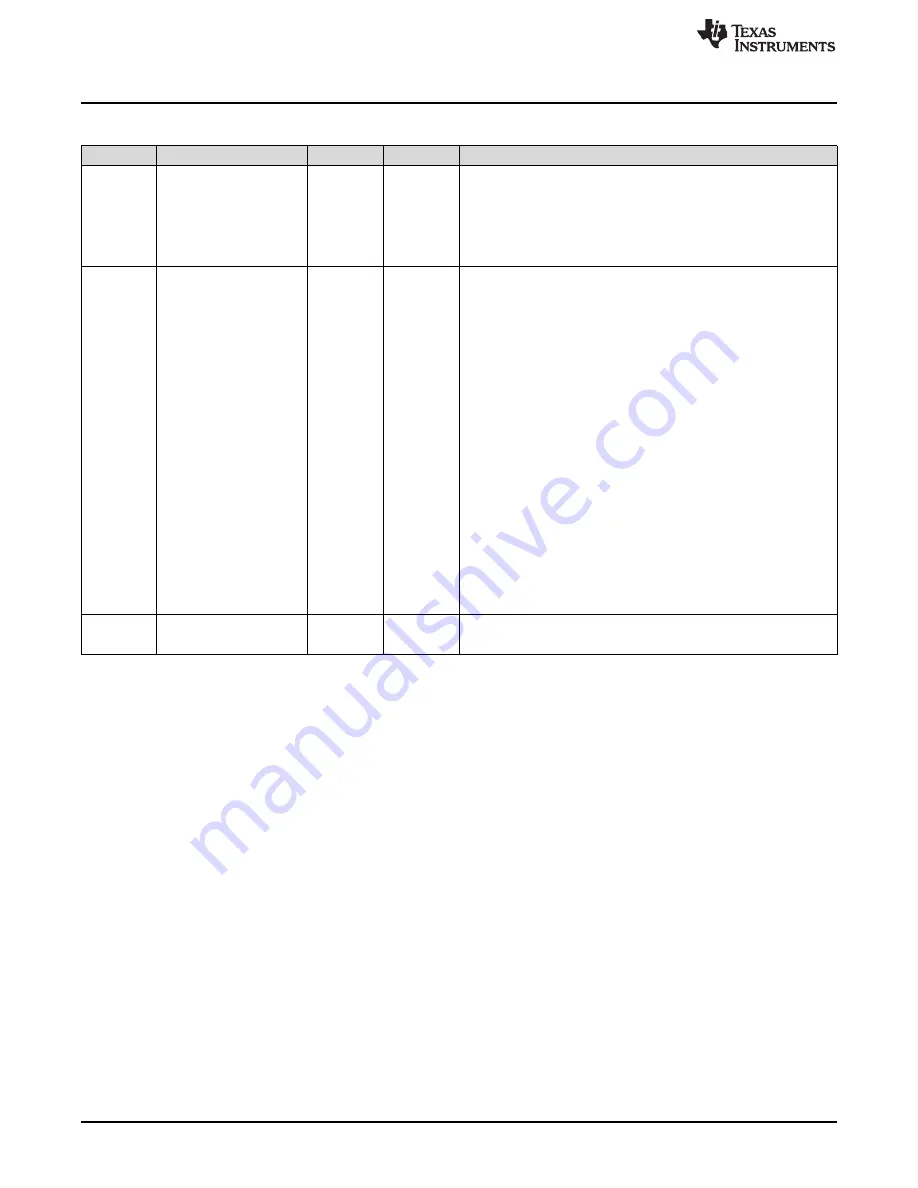

Table 8-5. GCCTL0 Register Field Descriptions (continued)

Bit

Field

Type

Reset

Description

3

ACCTEIE

R/W

0h

Enable NMI event for the Access time error flag (ACCTEIFG).

Reset type: BOR

0h (R/W) = ACCTEIE_0 : Disable NMI for the Access time error flag

(ACCTEIFG).

1h (R/W) = ACCTEIE_1 : Enable NMI for the Access time error flag

(ACCTEIFG). Generates vector in SYSSNIV.

2

FRPWR

R/W

1h

FRAM Memory Power Control Request

While the device is in AM (Active mode), the FRAM memory power

is controlled by the FRPWR bit and FRAM access. When the

FRPWR is set, the FRAM memory is in ACTIVE mode. When the

FRPWR is cleared by CPU, the FRAM memory goes into INACTIVE

mode so that the FRAM memory does not consumes power. The

INACTIVE mode can be used if no FRAM access is required for a

significant amount of time. Once the FRAM memory is in the

INACTIVE mode, wake-up is automatic. An access to FRAM (read or

write) will wake up the FRAM memory before performing the access.

In this case, the FRPWR bit is set automatically by the FRAM

controller. When the device enters LPM0/1/2/3/4 modes, the FRAM

memory also enters INACTIVE mode regardless of the FRPWR bit

status. When the device wakes up from LPM0/1/2/3/4, the FRAM

memory will be immediately powered up (ACTIVE mode) if the

FRPWR is set, but if the FRPWR bit is cleared, the FRAM memory

will remain in INACTIVE mode until the FRAM memory is actually

accessed (read or write). The latter case can be used to save the

device power consumption in case the device wakes up only for a

short amount of time, and the task during the wake-up can be

executed from RAM, so no need of FRAM access.

Reset type: PUC

0h (R/W) = FRPWR_0 : Enable INACTIVE mode.

1h (R/W) = FRPWR_1 : Enable ACTIVE mode.

1-0

Reserved

R

0h

Reserved. Always read 0.

Reset type: PUC