Information Manual

DSP1611/17/18/27/28/29 DIGITAL SIGNAL PROCESSOR

April 1998

JTAG Test Access Port

Lucent Technologies Inc.

DRAFT COPY

11-17

11.3 Elements of the JTAG Test Logic

(continued)

11.3.6 The Device Identification Register—JIDR (continued)

A description of each field for the DSP1617/18/27/28/29 only follows:

The Manufacturer Identity Field: Bits 11—0 of the JIDR make up the manufacturer identity field containing a

compressed form of the JEDEC standard manufacturer's identification code. The assigned Lucent Technologies

identification code is 0x03B.

Part Number Field: Bits 18—12 contain the DSP1617/18/27/28/29 unique part number. The ROM code is con-

tained in bits 27—19.

The Version Field: Bits 31—28 contain the RESERVED, SECURE, and CLOCK fields as described in

.

A DR-scan cycle of the JIDR produces a 32-bit binary pattern with the LSB being shifted out first from the TDO dur-

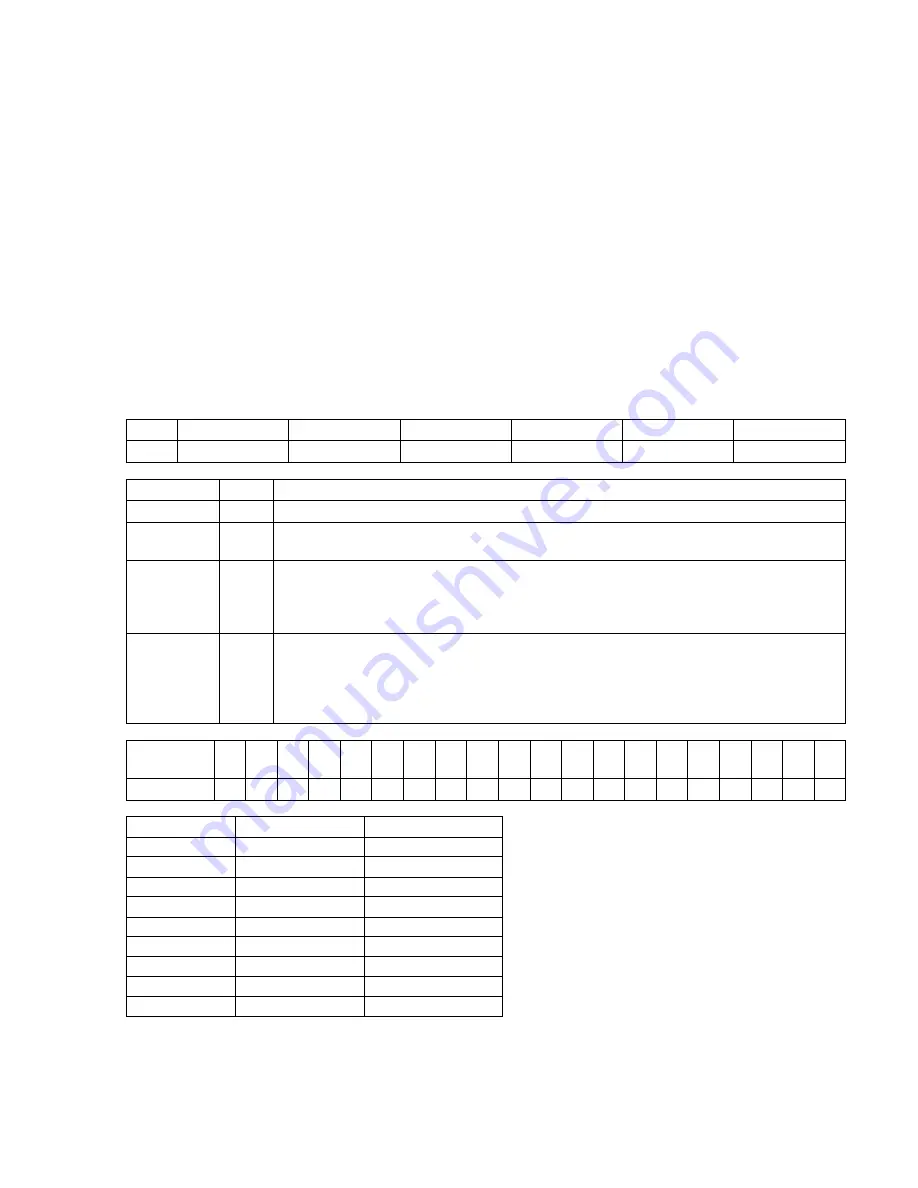

ing the shift-DR state. The following table summarizes the fields of JIDR for the DSP1617/18/27/28/29 only.

Table 11-5. JIDR Field Descriptions DSP1617/18/27/28/29

Bit

31

30

29—28

27—19

18—12

11—0

Field

RESERVED

SECURE

CLOCK

ROMCODE

PART ID

0x03B

Field

Value

Mask-Programmable Features

RESERVED

0

SECURE

0

1

Nonsecure ROM option.

Secure ROM option.

CLOCK

00

01

10

11

TTL level input clock option.

Small-signal input clock option.

Crystal oscillator input clock option.

CMOS level input clock option.

ROMCODE

—

Users ROMCODE ID:

The ROMCODE ID is the 9-bit binary value of the following expression:

(20 x value for first letter) + (value of second letter), where the values of the letters are in

the following table. For example, ROMCODE GK is

(20 x 6) + (9) = 129 or 0 1000 0001.

ROMCODE

LETTER

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

S

T

U

W

Y

VALUE

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

PART ID

Part ID (HEX)

Part ID (Binary)

DSP1617

0x18

0011000

DSP1618

0x19

0011001

DSP1618x24

0x1D

0011101

DSP1627

0x1C

0011100

DSP1627x32

0x2C

0101100

DSP1628x08

0x2A

0101010

DSP1628x16

0x2A

0101010

DSP1629x10

0x29

0101001

DSP1629x16

0x29

0101001

Summary of Contents for DSP1611

Page 18: ...Chapter 1 Introduction...

Page 27: ...Chapter 2 Hardware Architecture...

Page 52: ...Chapter 3 Software Architecture...

Page 116: ...Chapter 4 Instruction Set...

Page 154: ...Chapter 5 Core Architecture...

Page 176: ...Chapter 6 External Memory Interface...

Page 208: ...Chapter 7 Serial I O...

Page 237: ...Chapter 8 Parallel I O DSP1617 Only...

Page 261: ...Chapter 9 Parallel Host Interface PHIF DSP1611 18 27 28 29 Only...

Page 275: ...Chapter 10 Bit I O Unit...

Page 284: ...Chapter 11 JTAG Test Access Port...

Page 306: ...Chapter 12 Timer...

Page 313: ...Chapter 13 Bit Manipulation Unit...

Page 325: ...Chapter 14 Error Correction Coprocessor DSP1618 28 Only...

Page 350: ...Chapter 15 Interface Guide...

Page 367: ...Appendix A Instruction Encoding...

Page 379: ...Appendix B Instruction Set Summary...

Page 381: ...aD extractz aS IM16 B 52 aD insert aS arM B 53 aD insert aS IM16 B 54 aD aS aaT B 55...

Page 437: ...Index...