BUS INTERFACE UNIT

3-20

An idle bus state may or may not drive the bus. An idle bus state following a bus read cycle con-

tinues to float the bus. An idle bus state following a bus write cycle continues to drive the bus.

The BIU drives no control strobes active in an idle state except to indicate the start of another bus

cycle.

3.5 BUS CYCLES

There are four basic types of bus cycles: read, write, interrupt acknowledge and halt. Interrupt

acknowledge and halt bus cycles define special bus operations and require separate discussions.

Read bus cycles include memory, I/O and instruction prefetch bus operations. Write bus cycles

include memory and I/O bus operations. All read and write bus cycles have the same basic format.

The following sections present timing equations containing symbols found in the data sheet. The

timing equations provide information necessary to start a worst-case design analysis.

3.5.1 Read Bus Cycles

Figure 3-19 illustrates a typical read cycle. Table 3-2 lists the three types of read bus cycles.

Figure 3-20 illustrates a typical 16-bit interface connection to a read-only device interface. The

same example applies to an 8-bit bus system, except that no devices connect to an upper bus. Four

parameters (Table 3-3) must be evaluated when determining the compatibility of a memory (or

I/O) device. T

ADLTCH

defines the delay through the address latch.

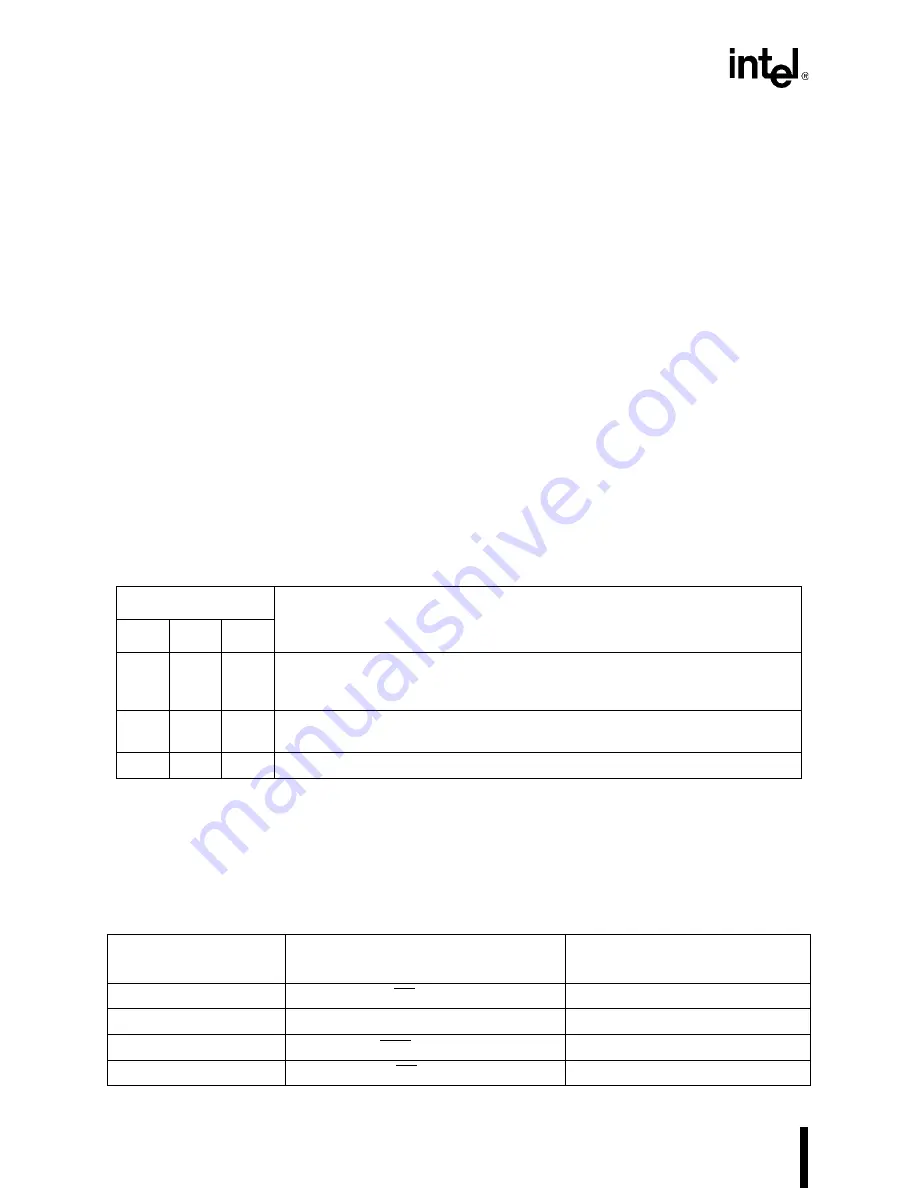

Table 3-2. Read Bus Cycle Types

Status Bit

Bus Cycle Type

S2

S1

S0

0

0

1

Read I/O — Initiated by the Execution Unit for IN, OUT, INS, OUTS instructions

or by the DMA Unit. A19:16 are driven to zero (see Chapter 10, “Direct Memory

Access Unit”).

1

0

0

Instruction Prefetch — Initiated by the BIU. Data read from the bus fills the

prefetch queue.

1

0

1

Read Memory — A19:0 select the desired byte or word memory location.

Table 3-3. Read Cycle Critical Timing Parameters

Memory Device

Parameter

Description

Equation

T

OE

Output enable (RD low) to data valid

2T – T

CLOV

2

– T

CLIS

T

ACC

Address valid to data valid

3T – T

CLOV

2

–T

ADLTCH

–

T

CLIS

T

CE

Chip enable (UCS) to data valid

3T – T

CLOV

2

– T

CLIS

T

DF

Output disable (RD high) to output float

T

RHAX

Summary of Contents for 80C186EA

Page 1: ...80C186EA 80C188EA Microprocessor User s Manual...

Page 2: ...80C186EA 80C188EA Microprocessor User s Manual 1995...

Page 19: ......

Page 20: ...1 Introduction...

Page 21: ......

Page 28: ...2 Overview of the 80C186 Family Architecture...

Page 29: ......

Page 79: ......

Page 80: ...3 Bus Interface Unit...

Page 81: ......

Page 129: ......

Page 130: ...4 Peripheral Control Block...

Page 131: ......

Page 139: ......

Page 140: ...5 ClockGenerationand Power Management...

Page 141: ......

Page 165: ......

Page 166: ...6 Chip Select Unit...

Page 167: ......

Page 190: ...7 Refresh Control Unit...

Page 191: ......

Page 205: ......

Page 206: ...8 Interrupt Control Unit...

Page 207: ......

Page 239: ...INTERRUPT CONTROL UNIT 8 32...

Page 240: ...9 Timer Counter Unit...

Page 241: ......

Page 265: ......

Page 266: ...10 Direct Memory Access Unit...

Page 267: ......

Page 295: ...DIRECT MEMORY ACCESS UNIT 10 28...

Page 296: ...11 Math Coprocessing...

Page 297: ......

Page 314: ...12 ONCE Mode...

Page 315: ......

Page 318: ...A 80C186 Instruction Set Additions and Extensions...

Page 319: ......

Page 330: ...B Input Synchronization...

Page 331: ......

Page 334: ...C Instruction Set Descriptions...

Page 335: ......

Page 383: ...INSTRUCTION SET DESCRIPTIONS C 48...

Page 384: ...D Instruction Set Opcodes and Clock Cycles...

Page 385: ......

Page 408: ...Index...

Page 409: ......