5-23

CLOCK GENERATION AND POWER MANAGEMENT

5.2.4 Implementing a Power Management Scheme

Table 5-2 summarizes the power management options available to the user. With three ways

available to reduce power consumption, here are some guidelines:

•

Powerdown mode reduces power consumption by several orders of magnitude. If the

application goes into and out of Powerdown frequently, the power reduction can probably

offset the relatively long intervals spent leaving Powerdown mode.

•

If background CPU tasks are usually necessary and the overhead of reprogramming

peripherals is not severe, Power-Save mode can “tune” the clock rate to the best value.

Remember that current varies linearly with respect to frequency.

•

Idle mode fits DMA-intensive and interrupt-intensive (as opposed to CPU-intensive) appli-

cations perfectly.

The processor can operate in Power-Save mode and Idle mode concurrently. With Idle mode

alone, rated power consumption typically drops a third or more. Power-Save mode multiplies that

reduction further according to the selected clock divisor.

Overall power consumption has two parts: switching power dissipated by driving loads such as

the address/data bus, and device power dissipated internally by the microprocessor whether or not

it is connected to external devices. A power management scheme should consider loading as well

as the raw specifications in the processor's data sheet.

NOTE

If an NMI or external maskable interrupt service routine is used to enter a

power management mode, the interrupt request signal should be deasserted

before entering the power management mode.

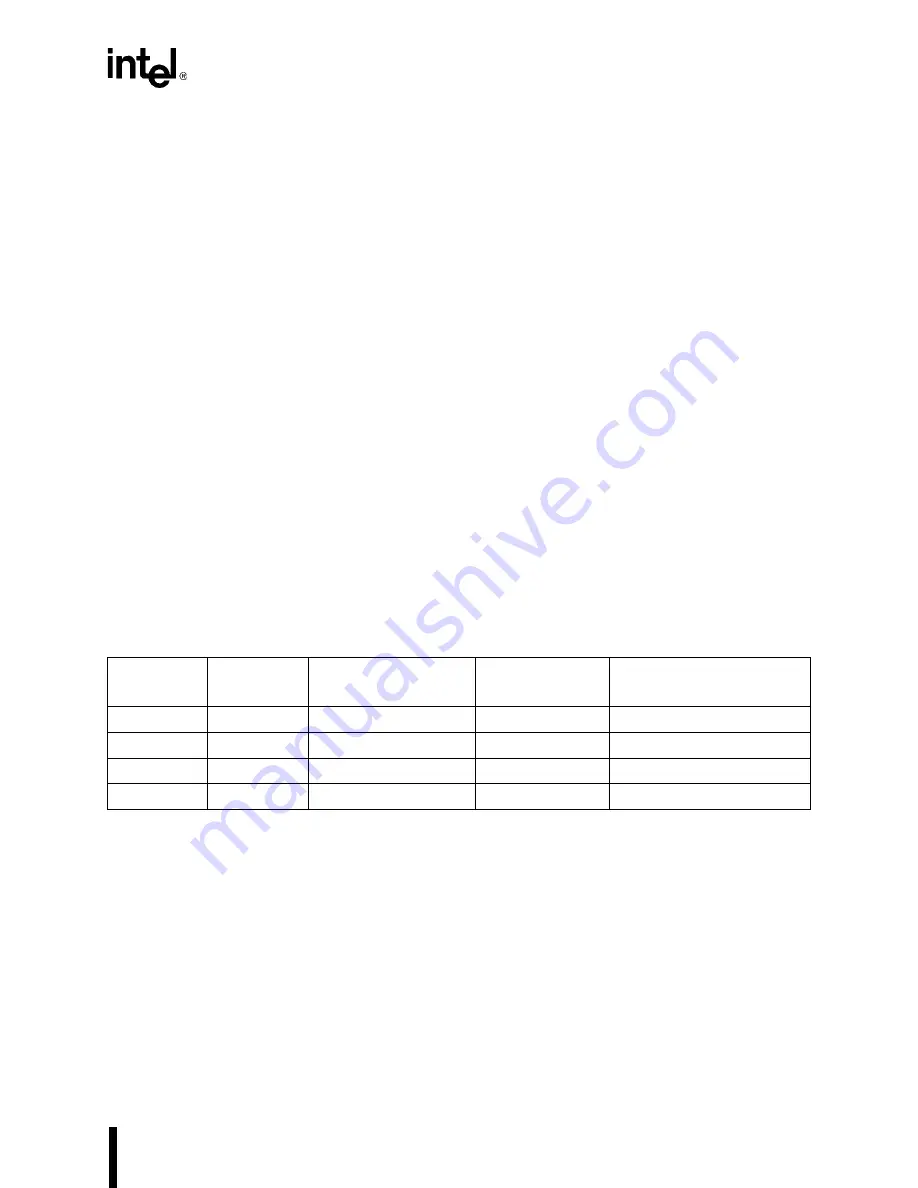

Table 5-2. Summary of Power Management Modes

Mode

Relative

Power

Typical

Power

User

Overhead

Chief

Advantage

Active

Full

250 mW at 16 MHz

—

Full-speed operation

Idle

Low

175 mW at 16 MHz

Low

Peripherals are unaffected

Power-Save

Adjustable

125 mW at 16/2 MHz

Moderate to High

Code execution continues

Powerdown

Lowest

250 µW

Low to Moderate

Long battery life

Summary of Contents for 80C186EA

Page 1: ...80C186EA 80C188EA Microprocessor User s Manual...

Page 2: ...80C186EA 80C188EA Microprocessor User s Manual 1995...

Page 19: ......

Page 20: ...1 Introduction...

Page 21: ......

Page 28: ...2 Overview of the 80C186 Family Architecture...

Page 29: ......

Page 79: ......

Page 80: ...3 Bus Interface Unit...

Page 81: ......

Page 129: ......

Page 130: ...4 Peripheral Control Block...

Page 131: ......

Page 139: ......

Page 140: ...5 ClockGenerationand Power Management...

Page 141: ......

Page 165: ......

Page 166: ...6 Chip Select Unit...

Page 167: ......

Page 190: ...7 Refresh Control Unit...

Page 191: ......

Page 205: ......

Page 206: ...8 Interrupt Control Unit...

Page 207: ......

Page 239: ...INTERRUPT CONTROL UNIT 8 32...

Page 240: ...9 Timer Counter Unit...

Page 241: ......

Page 265: ......

Page 266: ...10 Direct Memory Access Unit...

Page 267: ......

Page 295: ...DIRECT MEMORY ACCESS UNIT 10 28...

Page 296: ...11 Math Coprocessing...

Page 297: ......

Page 314: ...12 ONCE Mode...

Page 315: ......

Page 318: ...A 80C186 Instruction Set Additions and Extensions...

Page 319: ......

Page 330: ...B Input Synchronization...

Page 331: ......

Page 334: ...C Instruction Set Descriptions...

Page 335: ......

Page 383: ...INSTRUCTION SET DESCRIPTIONS C 48...

Page 384: ...D Instruction Set Opcodes and Clock Cycles...

Page 385: ......

Page 408: ...Index...

Page 409: ......