B-1

APPENDIX B

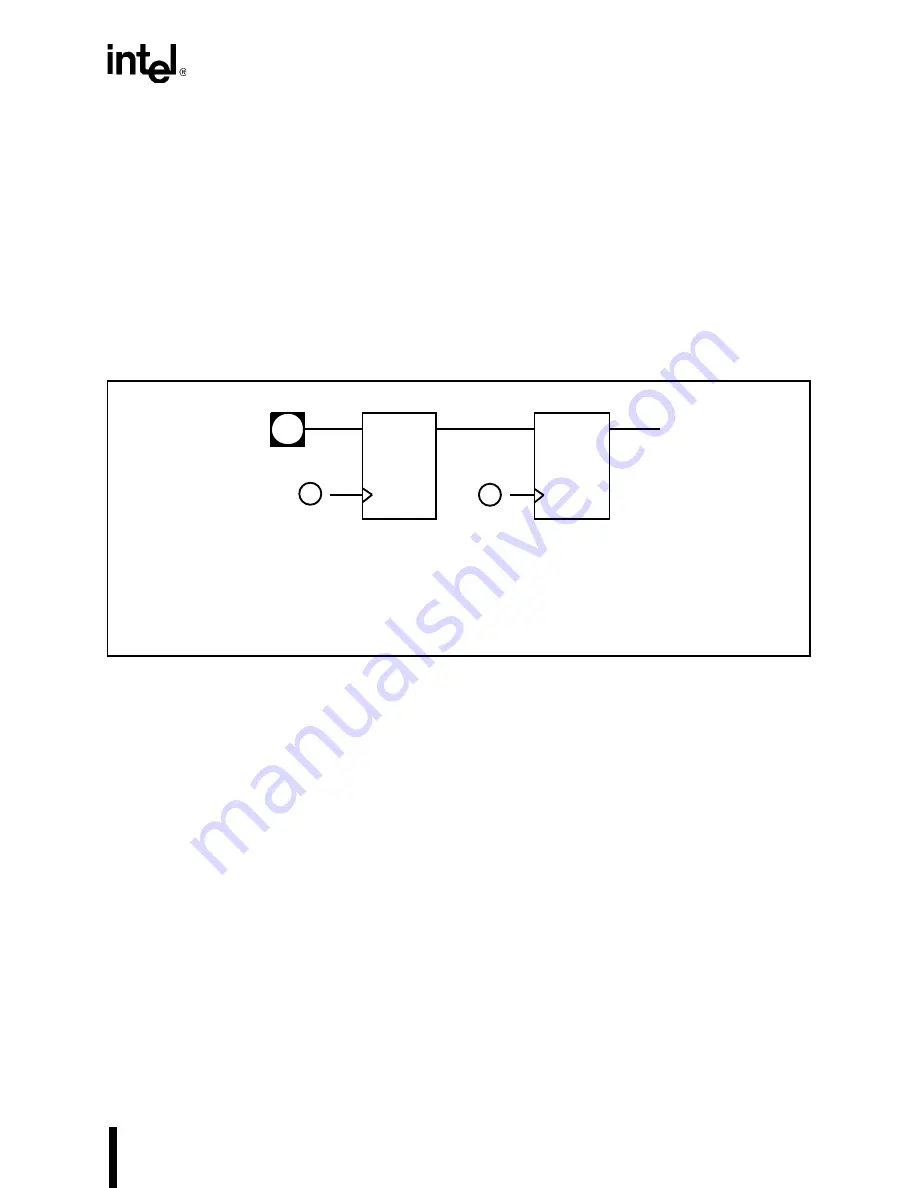

INPUT SYNCHRONIZATION

Many input signals to an embedded processor are asynchronous. Asynchronous signals do not re-

quire a specified setup or hold time to ensure the device does not incur a failure. However, asyn-

chronous setup and hold times are specified in the data sheet to ensure recognition. Associated

with each of these inputs is a synchronizing circuit (see Figure B-1) that samples the asynchro-

nous signal and synchronizes it to the internal operating clock. The output of the synchronizing

circuit is then safely routed to the logic units.

Figure B-1. Input Synchronization Circuit

B.1 WHY SYNCHRONIZERS ARE REQUIRED

Every data latch requires a specific setup and hold time to operate properly. The duration of the

setup and hold time defines a window during which the device attempts to latch the data. If the

input makes a transition within this window, the output may not attain a stable state. The data

sheet specifies a setup and hold window larger than is actually required. However, variations in

device operation (e.g., temperature, voltage) require that a larger window be specified to cover

all conditions.

Should the input to the data latch make a transition during the sample and hold window, the out-

put of the latch eventually attains a stable state. This stable state must be attained before the sec-

ond stage of synchronization requires a valid input. To synchronize an asynchronous signal, the

circuit in Figure B-1 samples the input into the first latch, allows the output to stabilize, then sam-

ples the stabilized value into a second latch. With the asynchronous signal resolved in this way,

the input signal cannot cause an internal device failure.

D

Q

D

Q

Synchronized

Output

Asynchronous

Input

1. First latch sample clock, can be phase 1 or phase 2 depending on pin function.

2. Second latch sample clock, opposite phase of first latch sample clock

(e.g., if first latch is sampled with phase 1, the second latch is sampled with phase 2).

First

Latch

Second

Latch

NOTES:

2

1

A1007-0A

Summary of Contents for 80C186EA

Page 1: ...80C186EA 80C188EA Microprocessor User s Manual...

Page 2: ...80C186EA 80C188EA Microprocessor User s Manual 1995...

Page 19: ......

Page 20: ...1 Introduction...

Page 21: ......

Page 28: ...2 Overview of the 80C186 Family Architecture...

Page 29: ......

Page 79: ......

Page 80: ...3 Bus Interface Unit...

Page 81: ......

Page 129: ......

Page 130: ...4 Peripheral Control Block...

Page 131: ......

Page 139: ......

Page 140: ...5 ClockGenerationand Power Management...

Page 141: ......

Page 165: ......

Page 166: ...6 Chip Select Unit...

Page 167: ......

Page 190: ...7 Refresh Control Unit...

Page 191: ......

Page 205: ......

Page 206: ...8 Interrupt Control Unit...

Page 207: ......

Page 239: ...INTERRUPT CONTROL UNIT 8 32...

Page 240: ...9 Timer Counter Unit...

Page 241: ......

Page 265: ......

Page 266: ...10 Direct Memory Access Unit...

Page 267: ......

Page 295: ...DIRECT MEMORY ACCESS UNIT 10 28...

Page 296: ...11 Math Coprocessing...

Page 297: ......

Page 314: ...12 ONCE Mode...

Page 315: ......

Page 318: ...A 80C186 Instruction Set Additions and Extensions...

Page 319: ......

Page 330: ...B Input Synchronization...

Page 331: ......

Page 334: ...C Instruction Set Descriptions...

Page 335: ......

Page 383: ...INSTRUCTION SET DESCRIPTIONS C 48...

Page 384: ...D Instruction Set Opcodes and Clock Cycles...

Page 385: ......

Page 408: ...Index...

Page 409: ......