AT32F435/437

Series Reference Manual

2022.11.11

Page 304

Rev 2.03

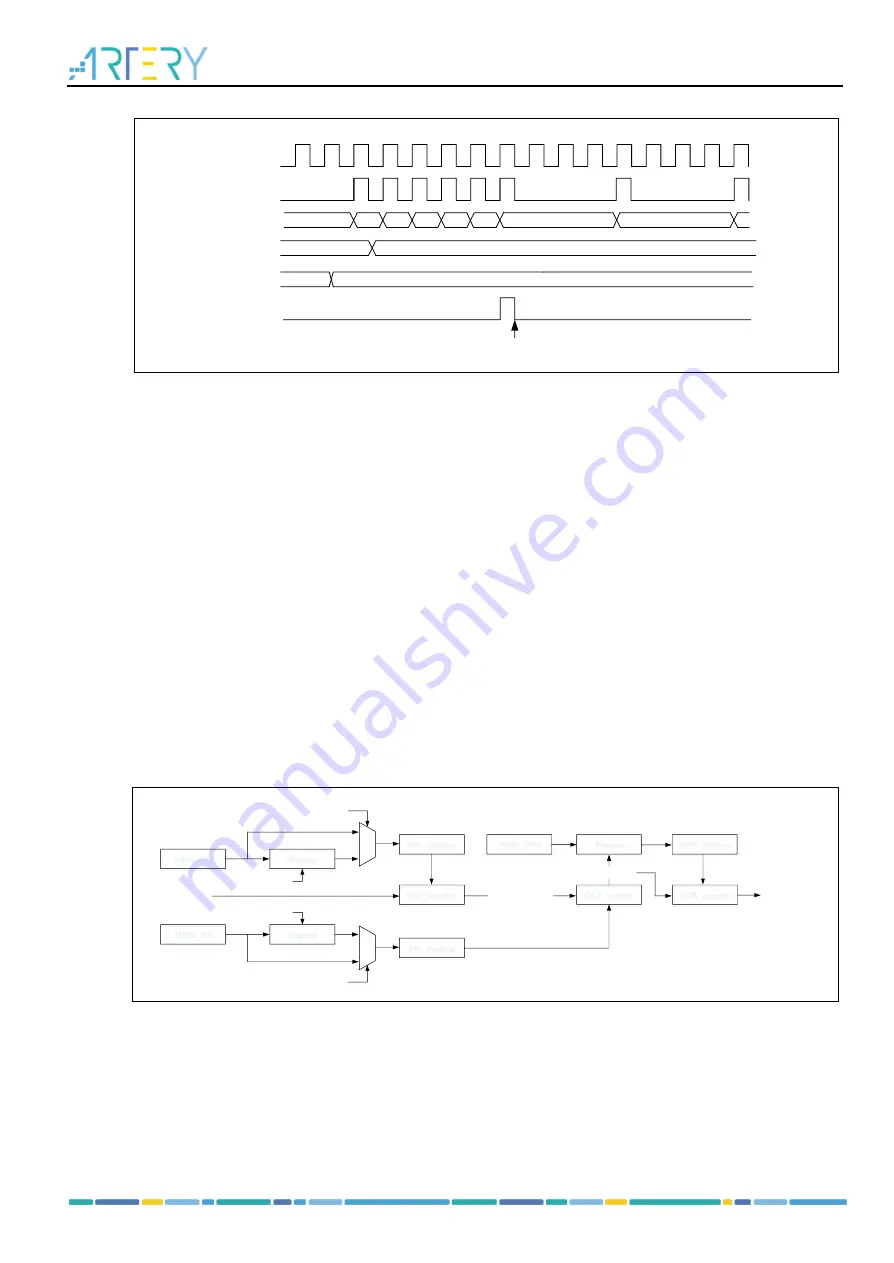

Figure 14-456

Counter timing with prescaler value changing from 1 to 4

TMR_CLK

CK_CNT

COUNTER

OVFIF

DIV[15

:

0]

18

17

19

1A

1B

1C

0

3

00

01

Clear

PR[15

:

0]

1C

14.4.3.2 Counting mode

The advanced-control timer consists of an internal 16-bit counter supporting up, down, up/down counting

modes to meet different application scenarios.

The TMRx_PR register is used to set the counting period. The value in the TMRx_PR is immediately

moved to the shadow register by default. When the periodic buffer is enabled (PRBEN=1), the value in

the TMRx_PR register is transferred to the shadow register only at an overflow event. The OVFEN and

OVFS bits are used to configure the overflow event.

The TMRx_DIV register is used to configure the counting frequency. The counter counts once every

count clock period (DIV[15:0]+1). Similar to the TMRx_PR register, when the periodic buffer is enabled,

the value in the TMRx_DIV register is updated to the shadow register at an overflow event.

Reading the TMRx_CNT register returns to the current counter value, and writing to the TMRx_CNT

register updates the current counter value to the value being written.

An overflow event is generated by default. Set OVFEN=1 in the TMRx_CTRL1 to disable generation of

update events. The OVFS bit in the TMRx_CTRL1 register is used to select overflow event source. By

default, counter overflow/underflow, setting OVFSWTR bit and the reset signal generated by the slave

timer controller in reset mode trigger the generation of an overflow event. When the OVFS bit is set, only

counter overflow/underflow triggers an overflow event.

Setting TMREN=1 to enable the timer to start counting. Base on synchronization logic, however, the

actual enable signal TMR_EN is set 1 clock cycle after the TMREN is set.

Figure 14-467

Counter structure

Overflow event

(RPR_overflow)

Overflow event

TMRx_PR

Preload

Overflow event

PR_shadow

1

0

TMRx_DIV

Preload

PRBEN

DIV_shadow

0

1

PRBEN

DIV_counter

CNT_counter

RPR_counter

RPR_shadow

Preload

TMRx_RPR

CNT_overflow

TMR_CLK

DIV_overflow

Upcounting mode

Set CMSEL[1:0]=2’b00 and OWCDIR=1’b0 in the TMRx_CTRL1 register to enable upcounting mode. In

this mode, the counter counts from 0 to the value programmed in the TMRx_PR register, then restarts

from 0, and generates a counter overflow event, with the OVFIF bit being set to 1. If the overflow event

is disabled, the counter is no longer reloaded with the preload value and period value at a counter

overflow event, otherwise, the counter is updated with the preload value and period value on an overflow

event.