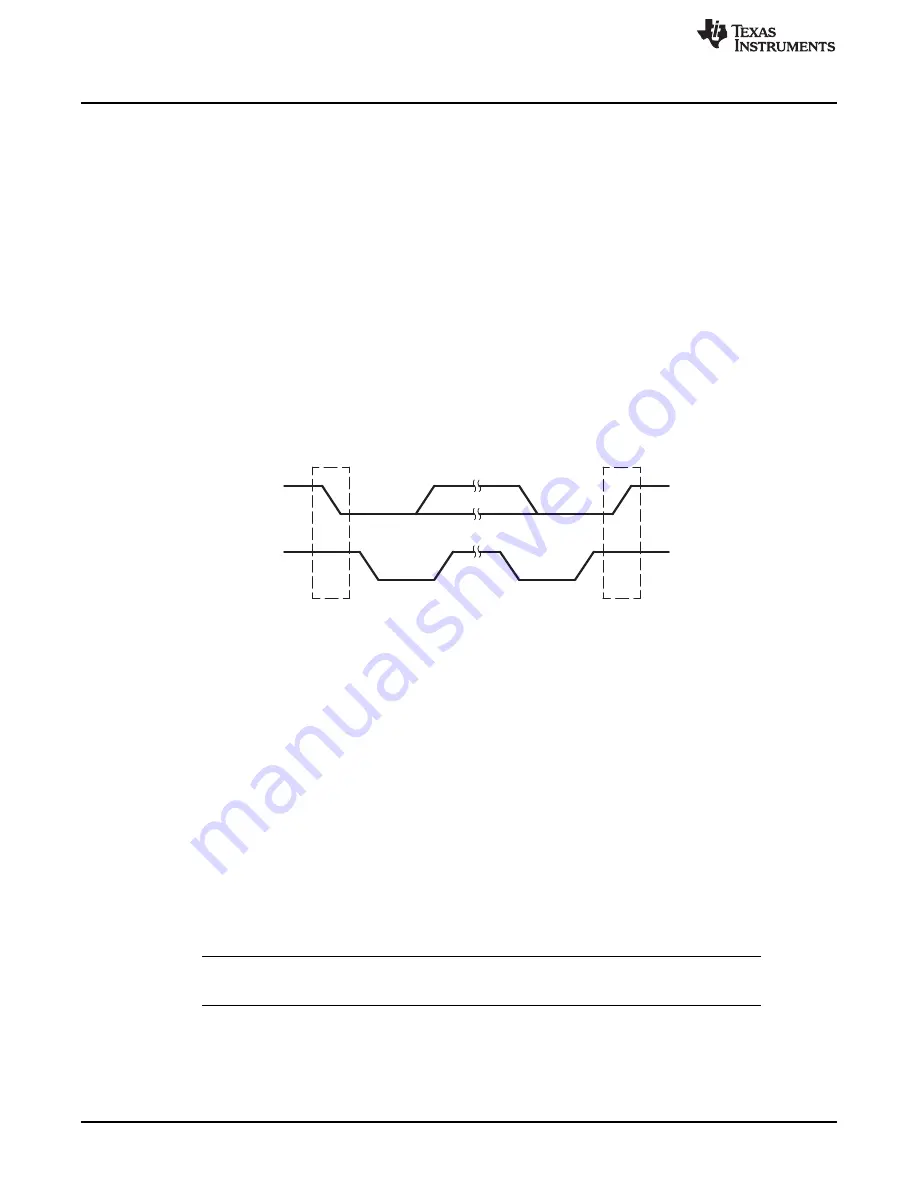

SDA

SCL

START

condition (S)

condition (P)

STOP

I2C Module Operational Details

1050

SPRUHE8E – October 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

C28 Inter-Integrated Circuit Module

To summarize, SCL will be held low in the following conditions:

•

When RSFULL = 1, in Slave-receiver mode.

•

When XSMT = 0, in Slave-transmitter mode.

I2C slave nodes have to accept and provide data when the I2C master node requests it.

•

To release SCL in slave-receiver mode, read data from I2CDRR.

•

To release SCL in slave-transmitter mode, write data to I2CDXR.

•

To force a release without handling the data, reset the module using the I2CMDR.IRS bit.

14.2.4 I2C Module START and STOP Conditions

START and STOP conditions can be generated by the I2C module when the module is configured to be a

master on the I2C-bus. As shown in

:

•

The START condition is defined as a high-to-low transition on the SDA line while SCL is high. A

master drives this condition to indicate the start of a data transfer.

•

The STOP condition is defined as a low-to-high transition on the SDA line while SCL is high. A master

drives this condition to indicate the end of a data transfer.

Figure 14-5. I2C Module START and STOP Conditions

After a START condition and before a subsequent STOP condition, the I2C-bus is considered busy, and

the bus busy (BB) bit of I2CSTR is 1. Between a STOP condition and the next START condition, the bus

is considered free, and BB is 0.

For the I2C module to start a data transfer with a START condition, the master mode bit (MST) and the

START condition bit (STT) in I2CMDR must both be 1. For the I2C module to end a data transfer with a

STOP condition, the STOP condition bit (STP) must be set to 1. When the BB bit is set to 1 and the STT

bit is set to 1, a repeated START condition is generated. For a description of I2CMDR and its bits

(including MST, STT, and STP), see

.

14.2.5 Serial Data Formats

shows an example of a data transfer on the I2C-bus. The I2C module supports 1 to 8-bit data

values. In

, 8-bit data is transferred. Each bit put on the SDA line equates to 1 pulse on the

SCL line, and the values are always transferred with the most significant bit (MSB) first. The number of

data values that can be transmitted or received is unrestricted. The serial data format used in

is the 7-bit addressing format. The I2C module supports the formats shown in

through

and described in the paragraphs that follow the figures.

NOTE:

In

through

, n = the number of data bits (from 1 to 8) specified by the

bit count (BC) field of I2CMDR.