CHAPTER 16 FLASH MEMORY (

µµµµ

PD70F3116)

735

User’s Manual U14492EJ3V0UD

16.5.3 RESET pin

When connecting the reset signals of the dedicated flash programmer to the RESET pin, which is connected, to the

reset signal generator on-board, a conflict of signals occurs. To avoid the conflict of signals, isolate the connection to

the reset signal generator.

When the reset signal is input from the user system in flash memory programming mode, the programming

operation will not be performed correctly. Therefore, do not input signals other than the reset signals from the

dedicated flash programmer.

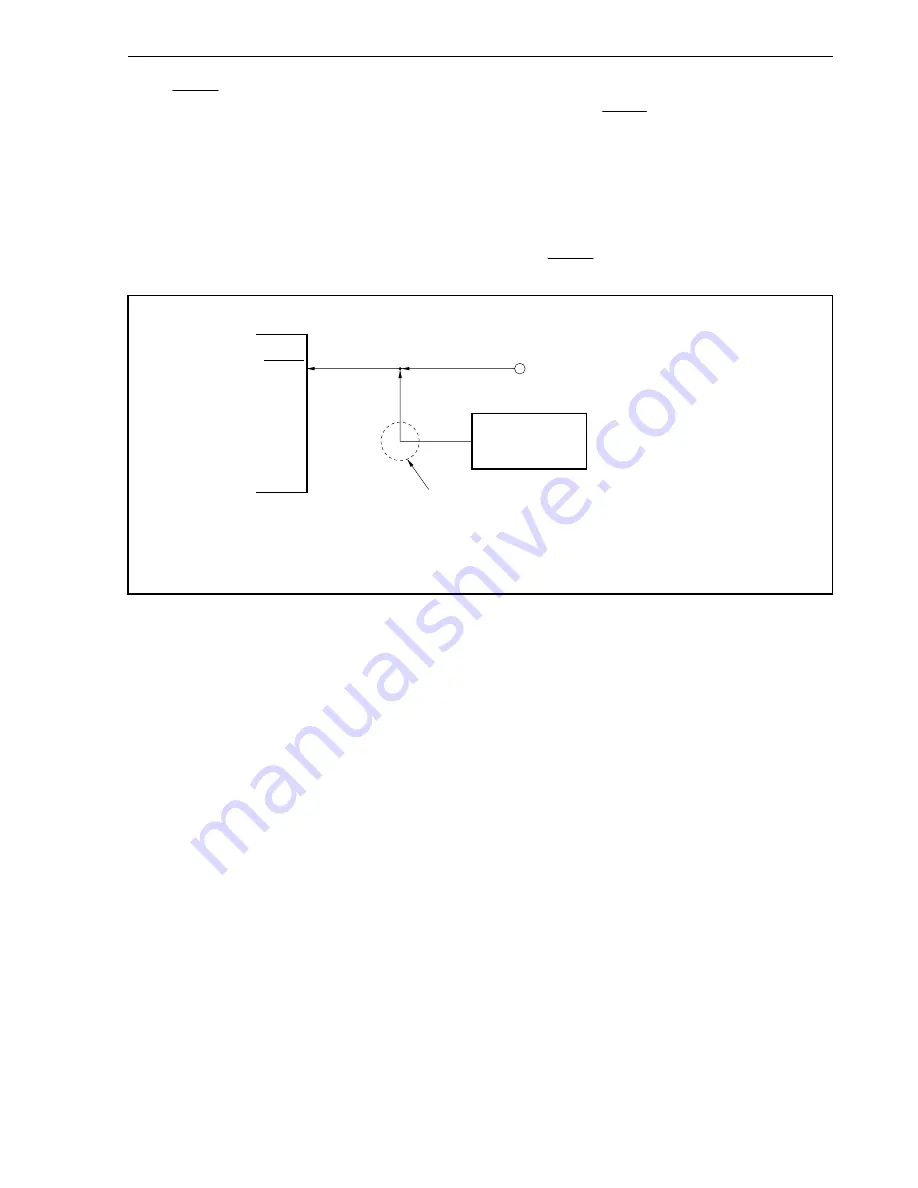

Figure 16-8. Conflict of Signals (RESET Pin)

V850E/IA1

RESET

Output pin

Reset signal generator

Dedicated flash programmer connection pin

Conflict of signals

In the flash memory programming mode, the signal

the reset signal generator outputs conflicts with the

signal the dedicated flash programmer outputs.

Therefore, isolate the signals on the reset signal

generator side.

16.5.4 NMI pin

Do not change the input signal to the NMI pin in flash memory programming mode. If it is changed in flash memory

programming mode, programming may not be performed correctly.

16.5.5 MODE0 to MODE2 pins

To shift to the flash memory programming mode, set MODE0 to high-level or low-level input, MODE1 to high-level

input, and MODE2 to low-level input, apply the writing voltage (7.8 V) to the V

PP

pin, and release reset.

16.5.6 Port pins

When the flash memory programming mode is set, all the port pins except the pins which communicate with the

dedicated flash programmer become output high-impedance status. Nothing need be done to these port pins. If

problems such as disabling output high-impedance status should occur to the external devices connected to the ports,

connect them to V

DD5

or V

SS5

via resistors.

16.5.7 Other signal pins

Connect X1 and X2 to the same status as in the normal operation mode.

The amplitude is 3.3 V.

Содержание V850E/IA1 mPD703116

Страница 2: ...2 User s Manual U14492EJ3V0UD MEMO...