CHAPTER 11 FCAN CONTROLLER

582

User’s Manual U14492EJ3V0UD

(2/4)

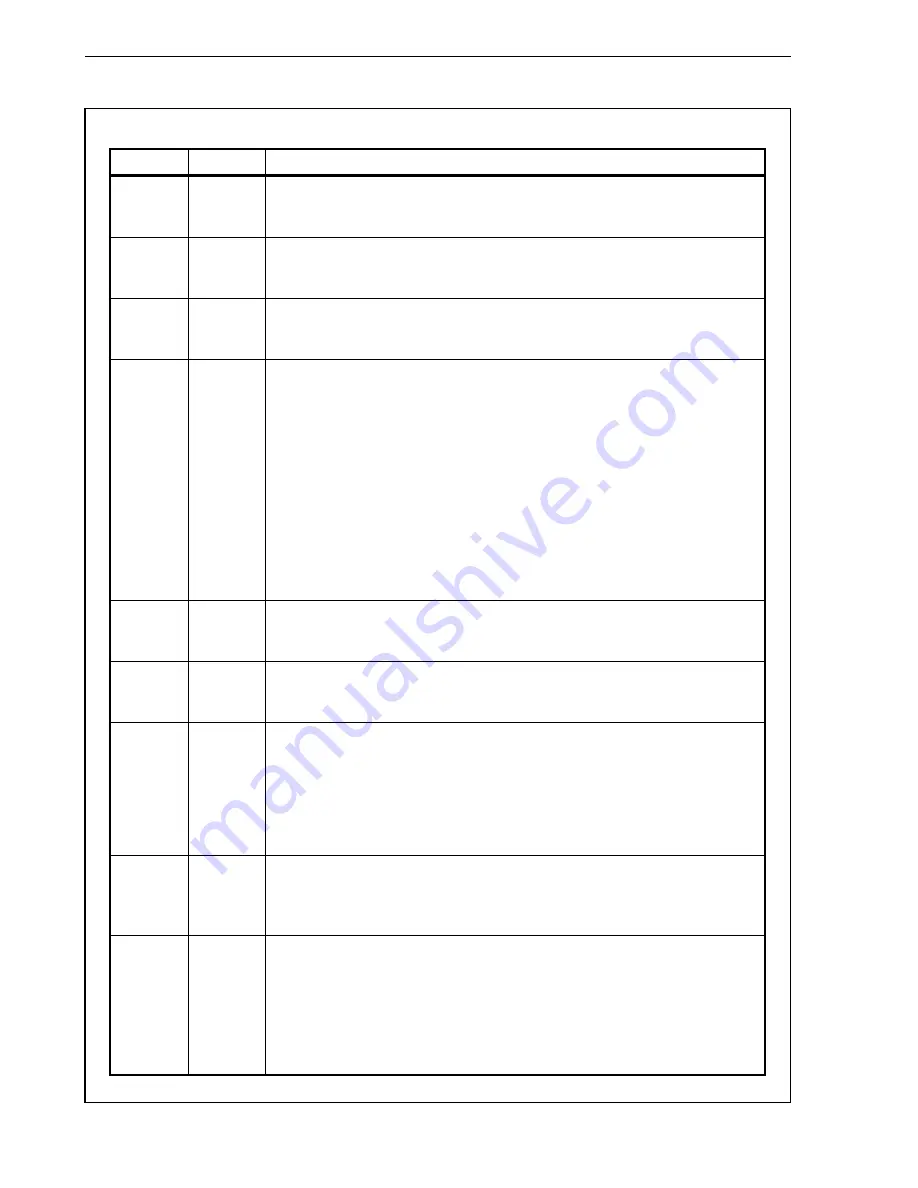

(a) Read (2/3)

Bit Position

Bit Name

Function

11

BOFF

This is the bus off status flag.

0: Transmit error counter < 256 (not bus off status)

1: Transmit error counter

≥

256 (bus off status)

10

TSTAT

This is the transmit status flag.

0: Transmission stopped status

1: Transmitting status

9

RSTAT

This is the receive status flag.

0: Reception stopped status

1: Receiving status

8

ISTAT

This is the initialization status flag.

0: Normal operating status

1: FCAN is stopped and initialized

Cautions 1. The ISTAT bit is set (to 1) when the CAN protocol layer acknowledges

the settings of the INIT and STOP bits. Also, this bit is automatically

cleared (to 0) when the INIT and STOP bits are cleared (to 0).

2. In the initialization status, “recessive” is output to the CTXD pin.

3. The C1SYNC and C1BRP registers can be written only in initialization

mode.

4. In the initialization status, the error counter (see 11.10 (23) CAN1 error

count register (C1ERC)) is cleared (to 0) and the error status (bits

TECS1, TECS0, RECS0, and RECS1) is reset.

6

DLEVR

This is the dominant level control bit for receive pins.

0: A low level to a receive pin is acknowledged as dominant

1: A high level to a receive pin is acknowledged as dominant

5

DLEVT

This is the dominant level control bit for transmit pins.

0: A low level is transmitted from a transmit pin as dominant

1: A high level is transmitted from a transmit pin as dominant

4

OVM

This is the overwrite mode control bit.

0: New messages stored in message buffer in which DN bit of M_STATn register (n = 00

to 31) is set

1: New messages in message buffer in which DN bit is set are discarded.

When the OVM bit = 1, the receive completion interrupt (INTCREC) is not generated even if

new messages are received in the message buffer in which the DN bit is set.

3

TMR

This is the time stamp control bit for reception.

0: Captures time stamp counter value when SOF is detected on CAN bus

1: Captures time stamp counter value when EOF is detected on CAN bus (a valid

message is confirmed)

2

STOP

This is the CAN stop mode control bit.

0: No CAN stop mode setting

1: CAN stop mode

The CAN stop mode can be selected only when the CAN module is set to CAN sleep mode

(the SLEEP bit is set (to 1)). CAN stop mode can be canceled only by the CPU (STOP bit

cleared (to 0)).

Содержание V850E/IA1 mPD703116

Страница 2: ...2 User s Manual U14492EJ3V0UD MEMO...