Chapter 2

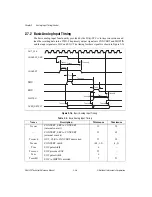

Analog Input Timing/Control

DAQ-STC Technical Reference Manual

2-78

©

National Instruments Corporation

AI_START1_Second_Irq_Enable

bit: 1

type: Write

in: Second_Irq_A_Enable_Register

address: 74

This bit enables the START1 interrupt in the secondary interrupt bank:

0: Disabled.

1: Enabled.

The START1 interrupt is generated on valid START1 triggers received by the DAQ-STC. A

valid START1 trigger is one that is received while the SC counter is armed and in the WAIT1

state.

AI_START1_Select

bits: <0..4>

type: Write

in: AI_Trigger_Select_Register

address: 63

This bitfield selects the START1 trigger:

0: Bitfield AI_START1_Pulse.

1–10: PFI<0..9>.

11–17: RTSI_TRIGGER<0..6>.

18: The internal signal G_OUT from general-purpose counter 0.

31: Logic low.

Related bitfields: AI_START1_Pulse.

AI_START1_St

bit: 7

type: Read

in: AI_Status_1_Register

address: 2

This bit indicates that a valid START1 trigger has been received by the DAQ-STC:

0: No.

1: Yes.

A valid START1 trigger is one that is received while the SC counter is armed and in the

WAIT1 state.

This bit can be cleared by setting AI_START1_Interrupt_Ack to 1. Related bitfields:

AI_SC_Arm, AI_START1_Interrupt_Ack. Refer to Table 8-2,

, for more information.

AI_START1_Sync

bit: 6

type: Write

in: AI_Trigger_Select_Register

address: 63

This bit enables internal synchronization of the START1 trigger to the SC source:

0: Disabled.

1: Enabled.

You should set this bit to 1 unless START1 is synchronized externally (to the signal selected

as the CONVERT source). You must set this bit to 1 if AI_START1_Select is set to 0. You

should set this bit to 0 if the ASIC is a START1 slave to another DAQ-STC. Related bitfields:

AI_START1_Select.