Chapter 2

Analog Input Timing/Control

DAQ-STC Technical Reference Manual

2-110

©

National Instruments Corporation

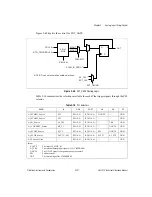

In external CONVERT mode, the external gate is synchronized to the active edge of

CONVERT_SRC. Figure 2-43 shows the timing for free-run gating mode with an external

CONVERT.

Figure 2-43.

Free-Run Gating Mode Timing, External CONVERT

The shaded areas in Figures 2-42 and 2-43 indicate where those signals would be asserted had

they not been gated off. The recognition of the external gate signal in the free-run gating mode

is relative to the START signal.

Name

Description

Minimum

Maximum

Tgtclki

External gate to SI2_Source setup internal

0

—

Tgtclke

External gate to CONVERT_SRC setup

external

5

—

All timing values are in nanoseconds.

CONVERT_SRC

START

CONVERT

External Gate

STOP

Tgtclke

Tgtclke