Chapter 2

Analog Input Timing/Control

DAQ-STC Technical Reference Manual

2-128

©

National Instruments Corporation

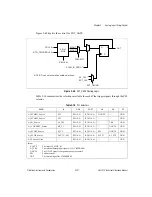

The SI2 load signal (SI2_LOAD) enables the SI2 counter to reload from the selected load

register on the next clock. SI2_LOAD is asserted when SI2_TC is reached or is asserted by

software.

The SI2 count enable signal (SI2_CE) allows the SI2 counter to count. SI2_CE is asserted on

any transition terminating at the CNT state, provided that the SI2 counter is armed.

The SI2 disarm signal (SI2_DISARM) clears the AI_SI2_Arm bit in the register map.

SI2_DISARM is asserted on the transition from the CNT state to the WAIT1 state when

AI_End_On_End_Of_Scan, AI_End_On_SC_TC, or AI_Trigger_Once is high.

Figure 2-51.

SI2 Control Circuit State Transitions

2.8.3.7 DIV Counter

The DIV counter is a 16-bit down counter. The DIV counter typically divides down

LOCALMUX_CLK when an external multiplexer is used. The DIV counter uses the same

clock that is selected for the SC counter (SC_SRC). The counter load register is directly

accessible from the register map. If the counter is disarmed, AI_DIV_Load will load the

counter with the value from the load register. During normal operation, the DIV counter will

synchronously reload from the load register following DIV_TC. The DIV control circuit

generates the count enable signals.

(AB)'

WAIT1

WAIT2

CNT

ABF

E' + M'

F'

ABF'

F

EMT'

A

B

E

F

G

H

I

J

M

N

SI_START1

AI_SI2_Arm

SI2_TC

START

SC_TC

AI_End_On_End_Of_Scan

AI_End_On_SC_TC

AI_Continuous

STOP

AI_Trigger_Once

T = G'H' + H'I'J

SI2_LOAD = E + AI_SI2_Load

SI2_CE = AI_SI2_Arm (CNT1(n+1))

S2I_DISARM = CNT(n) WAIT1(n+1) (H + I + N)

EMT