Chapter 3

Analog Output Timing/Control

DAQ-STC Technical Reference Manual

3-82

©

National Instruments Corporation

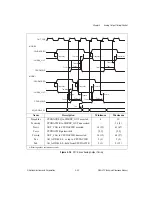

AO_UPDATE_Original_Pulse

bit: 7

type: Write

in: AO_Personal_Register

address: 78

If AO_UPDATE_Pulse_Timebase is 1, this bit determines the pulsewidth of the UPDATE

signal. The pulsewidth of the UPDATE signal is:

0: Equal to the pulsewidth of the signal used to generate the UPDATE signal, with the

maximum pulsewidth determined by AI_UPDATE_Pulse_Width.

1: Equal to the pulsewidth of the signal used to generate the UPDATE signal.

If you set this bit to 1, external gating for the analog output circuitry (except the UI2 counter)

will not work. Related bitfields: AO_UPDATE_Pulse_Timebase,

AO_UPDATE_Pulse_Width, AO_UPDATE_Source_Select.

AO_UPDATE_Output_Select

bits: <0..1>

type: Write

in: AO_Output_Control_Register

address: 86

This bitfield enables and selects the polarity of the UPDATE output signal:

0: High Z.

1: Ground.

2: Enable, active low.

3: Enable, active high.

This bitfield also selects the polarity of the PFI5/UPDATE output signal, if enabled for

output:

0: Active low.

1: Ground.

2: Active low.

3: Active high.

Related bitfields: BD_5_Pin_Dir.

AO_UPDATE_Pulse

bit: 0

type: Strobe

in: AO_Command_1_Register

address: 9

Setting this bit to 1 produces a pulse on the UPDATE and PFI5/UPDATE output signals if

the signals are enabled for output and if UPDATE pulses are not blocked. UPDATE pulses

can be blocked by the external gate or by AO_Software_Gate. The pulsewidth of the output

signals is determined by AO_UPDATE_Pulse_Width. This bit is cleared automatically.

Related bitfields: AO_UPDATE_Output_Select, AO_Software_Gate,

AO_UPDATE_Pulse_Width.