MAX32600 User’s Guide

Flash Controller and Instruction Cache

14.1 Registers (FLC)

• 0: Original flash access design; xaddr and yaddr are activated the same clock edge as SE

• 1: Inserts an additional clock cycle before SE is driven active (safety margin, slows down read accesses) (default)

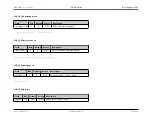

FLC_PERFORM.delay_se_en

Field

Bits

Default

Access

Description

delay_se_en

0

1

R/W

Delay SE Enable

• 0: Original flash access mode, 8-9 cycles for read access (default)

• 1: Fast read mode - the flash controller will perform back-to-back flash reads for an access time of 2-3 cycles per read cycle (after the 2nd)

14.1.1.7

FLC_STATUS

FLC_STATUS.debug_lock_window

Field

Bits

Default

Access

Description

debug_lock_window

0

s

R/O

Debug Locked - Hardware Window

• 0: No lockout from this source

• 1: The debug lockout is being asserted because the debug hardware window lockout feature is active, and the window of 1024 cycles following reset has not

yet elapsed.

FLC_STATUS.debug_lock_static

Field

Bits

Default

Access

Description

debug_lock_static

1

s

R/O

Debug Locked - Firmware Lockout

Rev.1.3 April 2015

Maxim Integrated

Page 657