MAX32600 User’s Guide

System Clock, Timers/Counters, Watchdog Timers and Real Time Clock

10.3 Real Time Clock (RTC)

• 1: One or more RTC transactions are pending as indicated by the associated _active flags in this register.

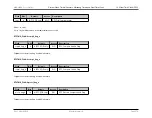

RTCTMR_CTRL.use_async_flags

Field

Bits

Default

Access

Description

use_async_flags

3

0 (RTC POR only)

R/W

Use Async RTC Flags

• 0: (default) Use flags synchronized to the core clock. This is redundant because they will get synchronized again by the digital core.

• 1: Connect flags synchronized to the RTC clock directly to the core, since they will be re-synchronized by the core. (This should have been the default setting

but currently is not.)

RTCTMR_CTRL.aggressive_rst

Field

Bits

Default

Access

Description

aggressive_rst

4

0 (RTC POR only)

R/W

Use Aggressive Reset Mode

• 0: (default) When resetting all of the RTC flags using the async_clear_flags bit, this bit will be cleared (reset condition released) on the next edge of the 4kHZ

RTC clock.

• 1: When resetting all of the RTC flags using async_clear_flags, the reset must be cleared asynchronously by firmware by manually clearing async_clear_flags

to 0.

When using the aggressive reset mode (=1), the reset must be released soon after the flag(s) have been set, to avoid the situation where the reset is released too

close to the next 4kHz clock edge, which may cause an unstable condition.

The purpose of this mode is to allow flags to be cleared properly in the situation where the prescaler compare is set to the shortest possible interval, which will cause

the prescaler compare to be tripped on every 4kHz clock cycle.

RTCTMR_CTRL.en_active

Rev.1.3 April 2015

Maxim Integrated

Page 570