MAX32600 User’s Guide

Trust Protection Unit (TPU)

11.3 Registers (TPU)

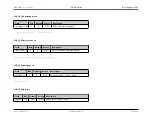

• 101b: divide by 32

• 110b: divide by 64

• 111b: Reserved

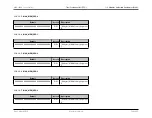

TPU_TSR_CTRL0.rtc_tx_busy

Field

Bits

Default

Access

Description

rtc_tx_busy

14

0b

R/O

RTC Domain Tx Busy

• 0: No RTC transfer in progress

• 1: Transfer in progress of this register to the RTC domain

TPU_TSR_CTRL0.lock

Field

Bits

Default

Access

Description

lock

15

0b

R/W

Lock Bit

Once set to 1, can only be cleared by BOR

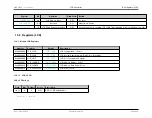

11.3.1.5

TPU_TSR_CTRL1

Default

Access

Description

0000 0000 0000 0000 0000 0000 0000 0000b

R/W

Dynamic Tamper Sensor Control 1

[bit 0] Dynamic tamper sensor DRS enable; set to 1 to enable a DRS output when the tamper sensor is triggered. Cleared to 0 on BOR only. May be written by

firmware only when the lock bit in TPU_TSR_CTRL0 is set to 0.

Rev.1.3 April 2015

Maxim Integrated

Page 629