MAX32600 User’s Guide

Analog Front End

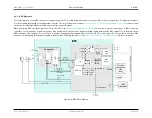

8.3 ADC

8.3.4.1

Peripheral Clock Configuration

The

MAX32600

supports multiple clock source options to operate the ADC.

To use the ADC, it is necessary to select the source for the ADC Peripheral Clock, select the clock divisor, and disable clock gating to generate the ADC Peripheral

Clock (PCLK).

Figure 8.7: ADC Peripheral Clock Configuration

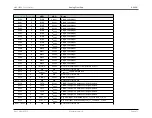

Input Clock Source Selection

The input clock to the ADC can be selected from the system clock, PLL generated clock, external high-frequency clock, external crystal direct input, or internal

24MHz relaxation oscillator. Using the external 8MHz crystal input directly will provide the optimal clock source and highest accuracy with the ADC. If an external

8MHz crystal is not available, it is recommended to use the PLL 8MHz output. Lower sampling rate(s) and input frequency signal(s) are less susceptible to aperture

jitter; thus, the relaxation oscillator can be used as the clock source in these applications. To select the ADC input clock source, set the register

as shown in the table below.

ADC Input Clock Source

00b

System Clock

Rev.1.3 April 2015

Maxim Integrated

Page 407