MAX32600 User’s Guide

Communication Peripherals

7.1 I²C

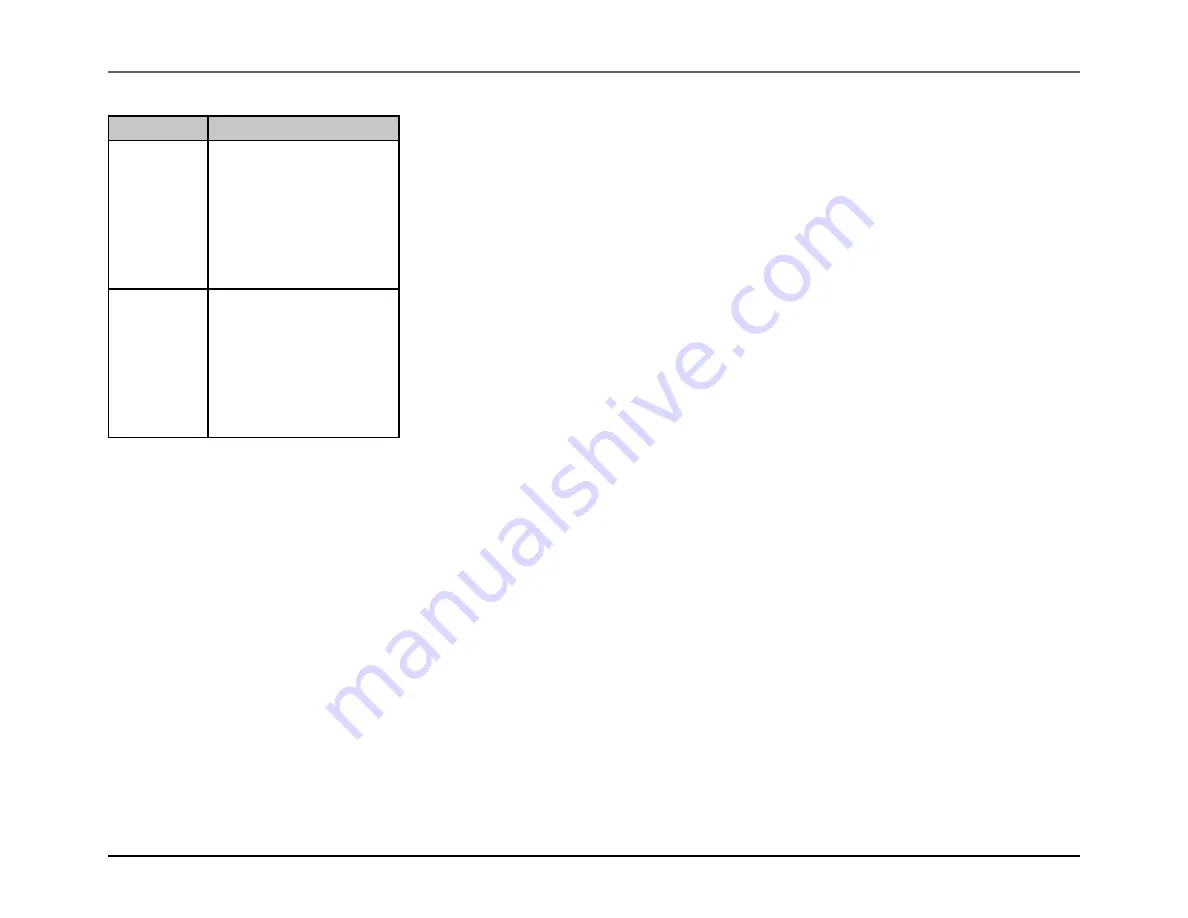

Logic Signal

Port and Pin

SDA

A) P2.4

B) P2.2

C) P7.4

D) P0.4

E) P2.6

F) P1.6

G) P7.6

H) P0.6

SCL

A) P2.5

B) P2.3

C) P7.5

D) P0.5

E) P2.7

F) P1.7

G) P7.7

H) P0.7

7.1.4

I²C Master Operation

Firmware defines I

2

C read and write operations via a transaction packet pushed onto the Master Transaction FIFO. I

2

C operation results are then read from Master

Results FIFO. An unexpected NACK on write data results in system interrupt. In this case, hardware can be opted to automatically issue a Stop under this condition

to free the bus. Results FIFO records the ACK/NACK status for each read data value received. Further, a full Results FIFO or empty Transaction FIFO will result in

clock stretching by master. There is a timeout feature which will issue a system interrupt if this delay exceeds a firmware controllable value (in ms). Loss of arbitration

in a multi-master system will result in a system interrupt.

Rev.1.3 April 2015

Maxim Integrated

Page 222