1-8 Technical Information

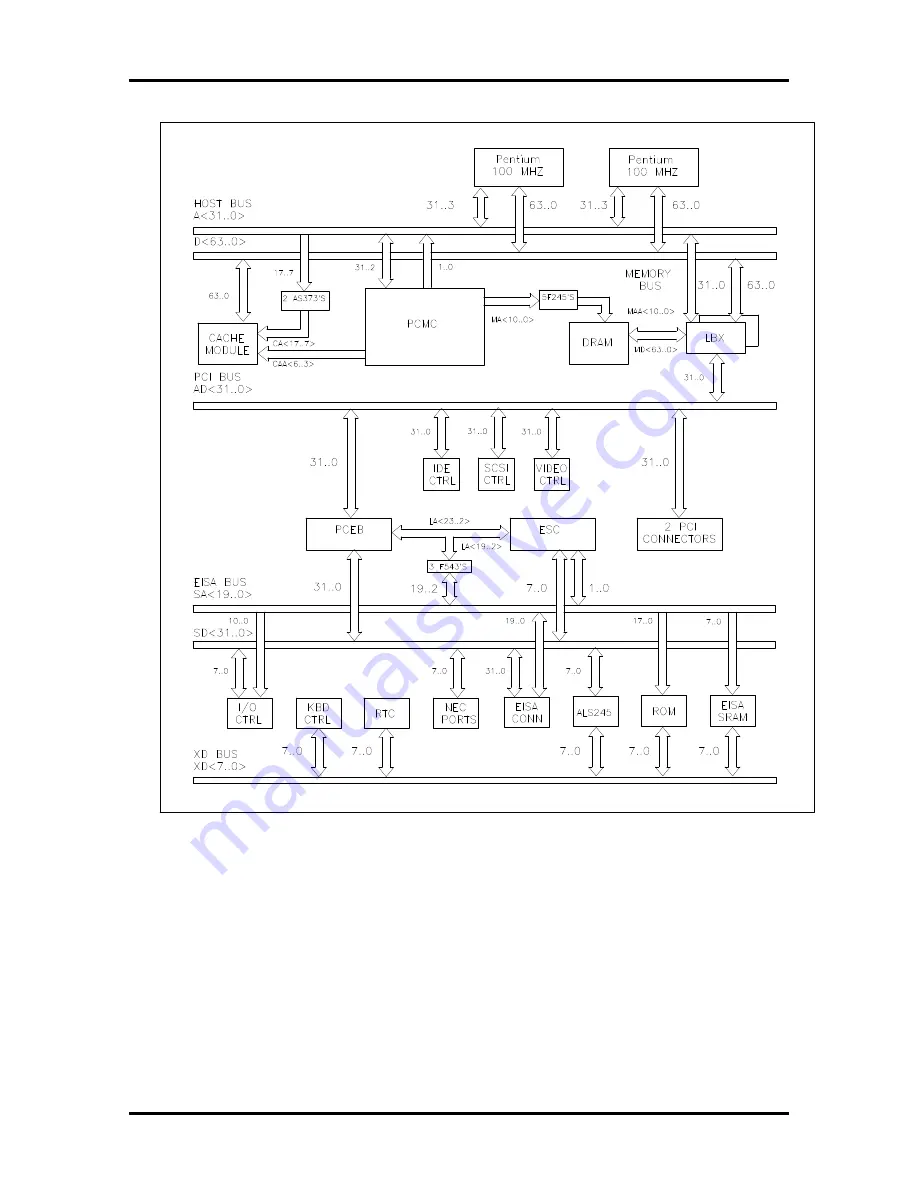

Figure Section 1-2 Component Block Diagram

Host Bus

The host bus consists of a 32-bit address bus (A<31..0>), a 64-bit data bus (D<63..0>), and

control circuitry. The host bus interfaces the processor to the PCI cache and memory

controller (PCMC), the local bus accelerators (LBXs), and the secondary (L2) cache. Host

bus cycles are initiated by ADS* signals from the processor and terminated by BRDY*

signal from the PCMC. All host bus cycles are monitored by the PCMC and directed to the

cache, system memory, or the PCI bus.