Connector Pin Assignments B-9

IDE INTERFACE CONNECTORS

All signal levels in the IDE interface are TTL compatible. A logic 1 is a signal whose volt-

age level is between 2.0 and 5.0 V. A logic 0 is a signal measuring between 0.00 V and

0.70 V.

The two system board IDE connectors are physically identical. Both are fast PCI local bus

IDE connectors. Table Appendix B-10 provides the IDE pin assignments. All signals on

the Host interface have the prefix HOST. All negatively active signals are further prefixed

with a “–” designation. All positively active signals are prefixed with a “+” designation.

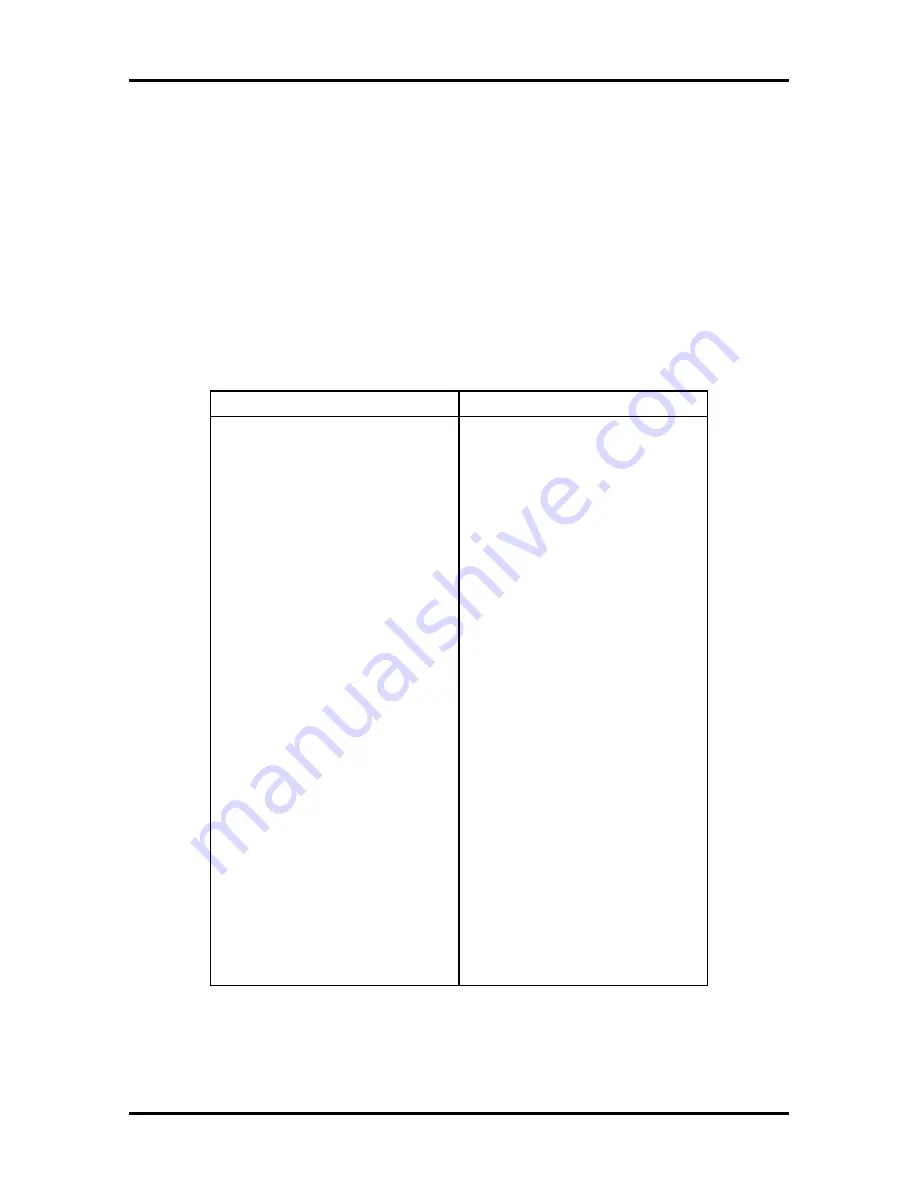

Table Appendix B-10 IDE Connector (J30/J32) Pin

Assignments

Pin

Signal

Pin

Signal

1

–HOST RESET

2

GND

3

+HOST DATA 7

4

+HOST DATA 8

5

+HOST DATA 6

6

+HOST DATA 9

7

+HOST DATA 5

8

+HOST DATA 10

9

+HOST DATA 4

10

+HOST DATA 11

11

+HOST DATA 3

12

+HOST DATA 12

13

+HOST DATA 2

14

+HOST DATA 13

15

+HOST DATA 1

16

+HOST DATA 14

17

+HOST DATA 0

18

+HOST DATA 15

19

GND

20

KEY

21

DRQ3

22

GND

23

–HOST IOW

24

GND

25

–HOST IOR

26

GND

27

IOCHRDY

28

+HOST ALE

29

–DACK3

30

GND

31*

+HOST IRQ14

32

–HOST IO16

33

+HOST ADDR 1

34

GND

35

+HOST ADDR 0

36

+HOST ADDR 2

37

–HOST CSO

38

–HOST CS1

39

–HOST SLV/ACT

40

GND

*The PCI IDE connector uses IRQ15