User Manual

170 of 562

V 1.0

2021-08-25

XDPP1100 technical reference manual

Digital power controller

Digital pulse width modulator

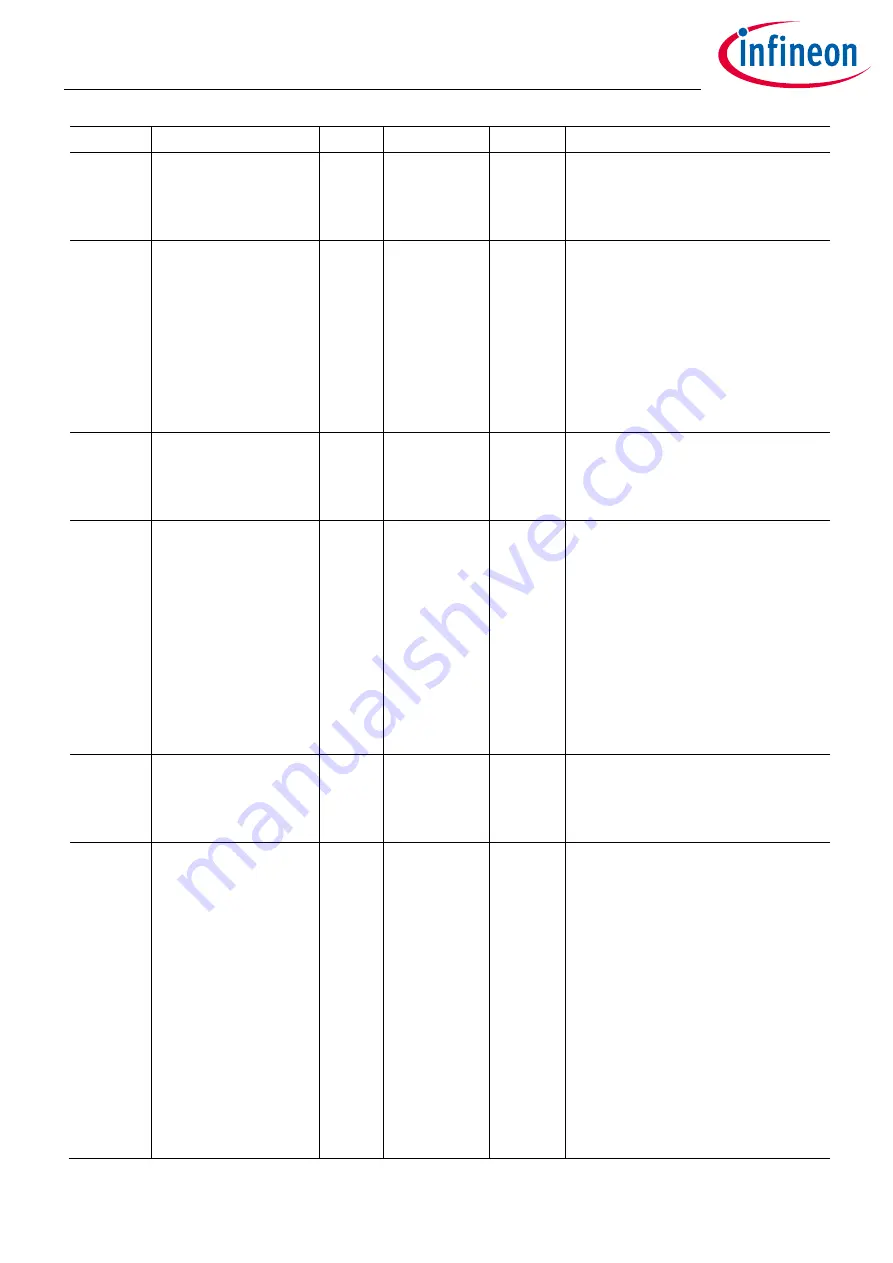

Peripheral Field name

Access Address

Bits

Description

pwm

ramp1_force_duty_e

n

RW

7000_2C48h [8]

PWM ramp1 forced duty-cycle

select.

0: Use PID computed duty cycle

1: Use ramp1_force_duty

pwm

ramp1_force_t1

RW

7000_2C4Ch [10:0]

PWM ramp1 forced t1 setting

selected by ramp1_force_t1_en. t1

is the time of the first PWM

“

edge

”

in a ramp cycle. In a TE modulation

scheme t1 is fixed at 0. In the

leading and DE modulation

schemes t1 is determined based on

the duty cycle.

LSB = 5 ns, range = 0 to 10235 ns

pwm

ramp1_force_t1_en

RW

7000_2C4Ch [11]

PWM ramp1 t1 force enable.

0: t1 determined by modulation

scheme and duty cycle

1: t1 set by ramp1_force_t1

pwm

ramp1_force_t2

RW

7000_2C50h [10:0]

PWM ramp1 forced t2 setting

selected by ramp1_force_t2_en. t2

is the time of the second PWM

“

edge

”

in a ramp cycle. In a LE

modulation scheme t2 is fixed at

T

switch

(or T

switch

/2 in bridge

topologies). In the trailing and DE

modulation schemes t2 is

determined based on the duty

cycle.

LSB = 5 ns, range = 0 to 10235 ns

pwm

ramp1_force_t2_en

RW

7000_2C50h [11]

PWM ramp1 t2 force enable.

0: t2 determined by modulation

scheme and duty cycle

1: t2 set by ramp1_force_t2

pwm

pwm1_dr

RW

7000_2C54h [7:0]

PWM1 rising edge delay (dead) time

from t1 or t2. Mapping of the rising

edge to t1 or t2 defined by

pwm1_rise_sel. In order to

synchronously update all pwmX_dr

and pwmX_df times

simultaneously, an update to any

dead time register only becomes

effective after 7000_2C80h

(pwm12_dr, pwm12_df) is written.

Computed by FW from PMBus

command as follows:

pwm1_dr[7:0] =

PWM_DEADTIME[15:8]