master transmits (sends) data to the selected slave, and a one in this position means that the master

receives data from the slave.

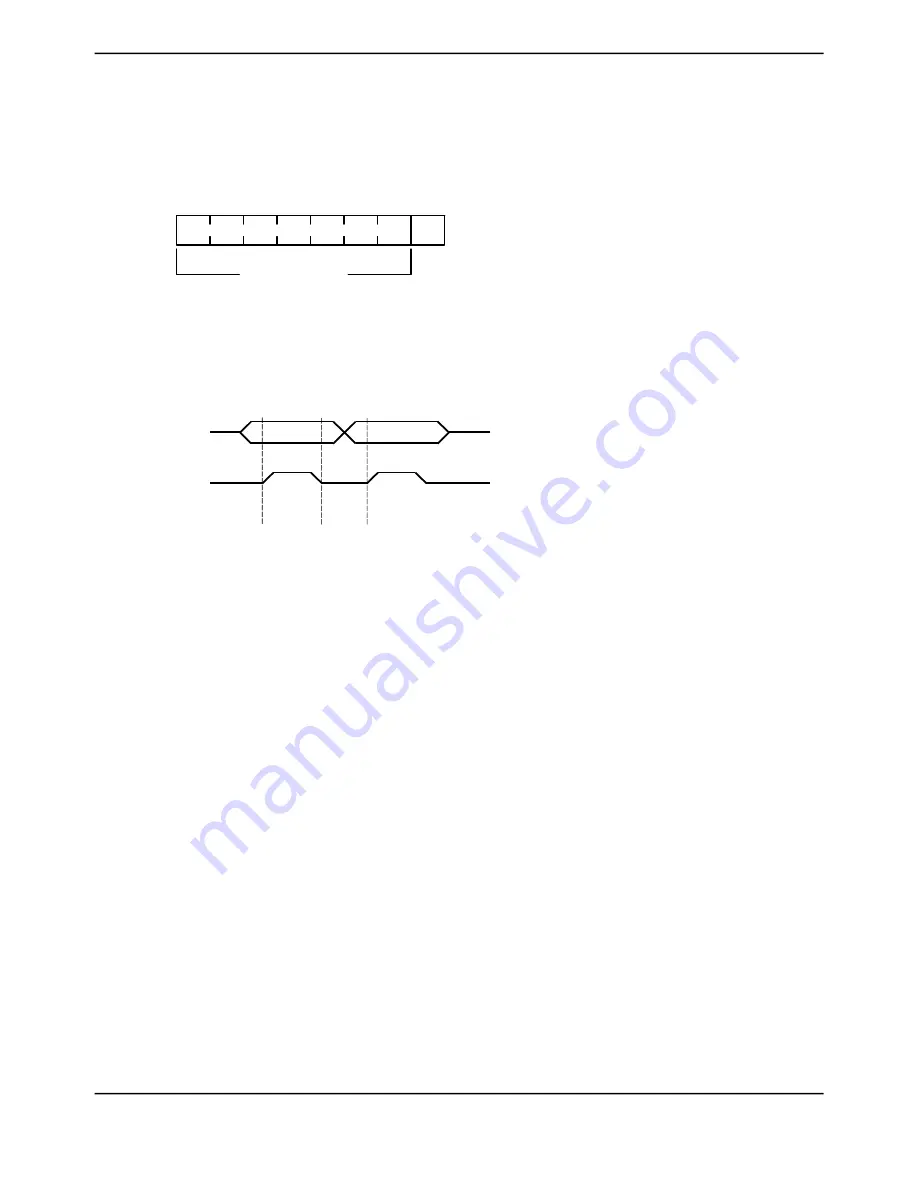

Figure 18-5. R/S Bit in First Byte

R/S

LSB

Slave address

MSB

18.3.1.3

Data Validity

The data on the SDA line must be stable during the high period of the clock, and the data line can

only change when SCL is Low (see Figure 18-6).

Figure 18-6. Data Validity During Bit Transfer on the I

2

C Bus

Change

of data

allowed

Data line

stable

SDA

SCL

18.3.1.4

Acknowledge

All bus transactions have a required acknowledge clock cycle that is generated by the master. During

the acknowledge cycle, the transmitter (which can be the master or slave) releases the SDA line.

To acknowledge the transaction, the receiver must pull down SDA during the acknowledge clock

cycle. The data transmitted out by the receiver during the acknowledge cycle must comply with the

data validity requirements described in “Data Validity” on page 1280.

When a slave receiver does not acknowledge the slave address, SDA must be left High by the slave

so that the master can generate a STOP condition and abort the current transfer. If the master

device is acting as a receiver during a transfer, it is responsible for acknowledging each transfer

made by the slave. Because the master controls the number of bytes in the transfer, it signals the

end of data to the slave transmitter by not generating an acknowledge on the last data byte. The

slave transmitter must then release SDA to allow the master to generate the STOP or a repeated

START condition.

If the slave is required to provide a manual ACK or NACK, the

I

2

C Slave ACK Control

(I2CSACKCTL)

register allows the slave to NACK for invalid data or command or ACK for valid

data or command. When this operation is enabled, the MCU slave module I

2

C clock is pulled low

after the last data bit until this register is written with the indicated response.

18.3.1.5

Repeated Start

The I

2

C master module has the capability of executing a repeated START (transmit or receive) after

an initial transfer has occurred.

A repeated start sequence for a Master transmit is as follows:

1.

When the device is in the idle state, the Master writes the slave address to the

I2CMSA

register

and configures the

R/S

bit for the desired transfer type.

June 18, 2014

1280

Texas Instruments-Production Data

Inter-Integrated Circuit (I

2

C) Interface