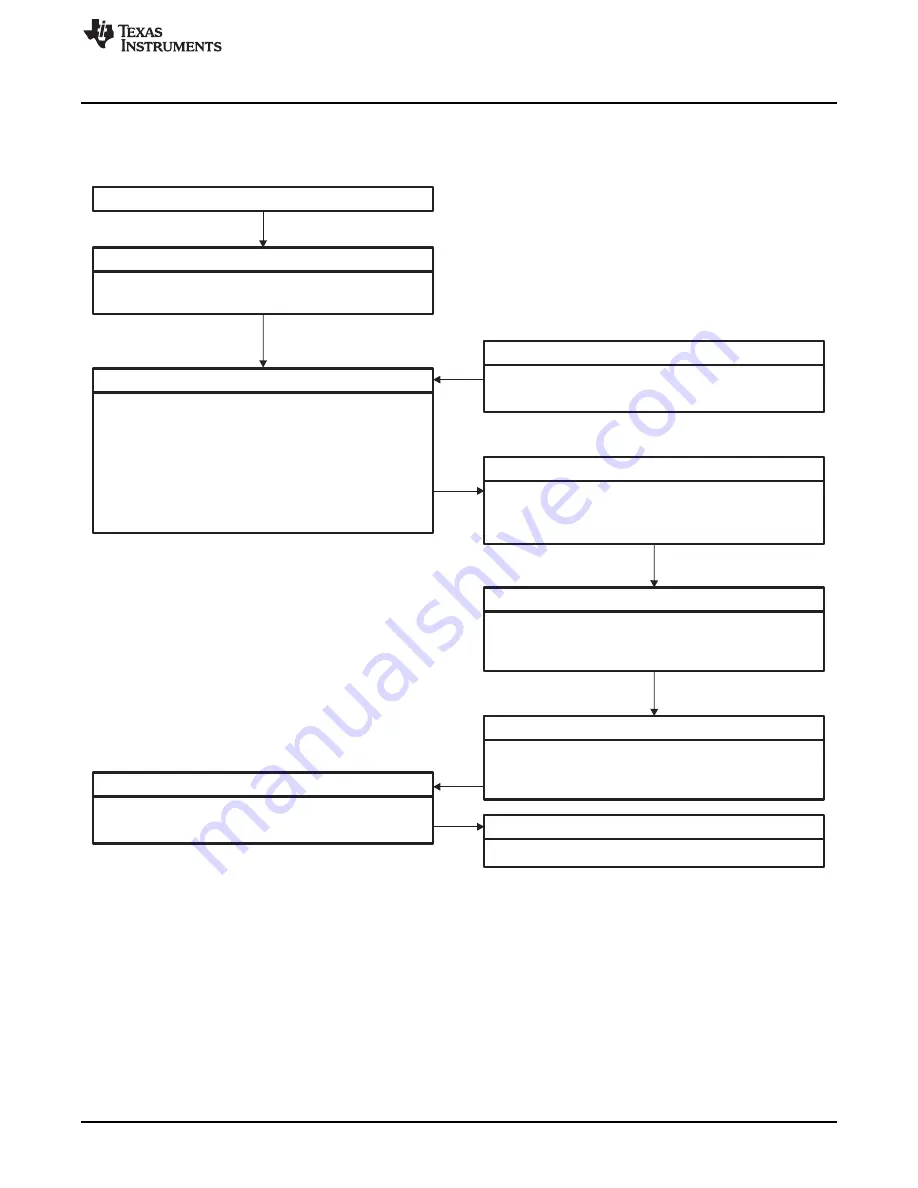

Hardware

SOC Peripheral Module

Step 1

M_IRQ_n Asserted

MPU INTC

If the IRQ_n is not masked and configured as an IRQ/FIQ,

the MPU_INTC_IRQ/MPU_INTC_FIQ line is asserted.

Step 2

MPU_INTC_IRQ/

MPU_INTC_FIQ Asserted

ARM Host Processor (Step 4)

If FIQs are enabled (F==0):

Finish the current instruction number N

Store address of next instruction to be

executed in the Link Register

Save CPSR before execution in the SPSR

Enter ARM FIQ mode

Disable IRQs and FIQs at ARM side

Execute the interrupt vector.

?

?

?

?

?

?

Software

Main Program

?

?

Execution of instruction number 1

Execution of instruction number N

ISR in IRQ/FIQ Mode (Step 5)

?

?

?

Save ARM critical context

Identify interrupt source

Branch to relevant interrupt subroutine handler

Relevant Subroutine Handler in IRQ/FIQ Mode (Step 6)

?

?

Handles the event (functional procedure)

Deassert the interrupt M_IRQ_n at SOC peripheral

module side.

ISR in IRQ/FIQ Mode (Step 7)

?

?

Allow a new IRQ/FIQ at INTC side by setting the

NEWIRQAGR/NEWFIQAGR bit to 1.

Restore ARM critical context.

Main Program

?

Execution of instruction number N + 1

ARM Host Processor (Step 8)

?

?

Restore the whole CPSR

Restore the PC

Branch

Branch

Branch

Return

Return

Basic Programming Model

Figure 6-2. IRQ/FIQ Processing Sequence

193

SPRUH73H – October 2011 – Revised April 2013

Interrupts

Copyright © 2011–2013, Texas Instruments Incorporated