2–16

Principles of Operation

CLOCK

GENERATION

8/4/2 MHZ

RESET

GENERATION

370 ms

BAUD RATE

XTAL OSC

HOST

INTERFACES

HOST

RS–232

HOST

DATA

PRODUCTS

CEN–

TRONICS

H

O

S

T

D

M

A

F

A

U

L

T

N

S

W

I

T

C

H

CLK

INTA INTERRUPT

INPUTS

CLK

NMC

8MHZ

RESET

HALT

RXD

DCD

DSR

CTS

TXD

RTS

DTR

REVCHNL

RX CLK

TX CLK

EXT CLK

GND

IDB8–IDB1

8

PI

IDSTB

IDRQ

IRDY

IONL

ICSTB

ICBUSY

IACK

ICPE

+5V

GND

CLK

ADDR

68000

CPU

DATA

CNTL

DTACK

H

O

S

T

D

M

A

A

D

D

R

E

S

S

(18)

(16)

ADDRESS

DECODE

BUS

ARBITRATION

CONTROL

CNTLS

DECODE

AND

BUFFER

DTACK

GENERATOR

DATA BUS

PARALLEL

I/F DMA

CONTROLLER

68B44

PARITY CHECK

CONTROL CODE DETECT

I/O

POLARITY

IDS

PARALLEL

I/F

CONTROL

SIGNALS

DATA

LATCHING

HOST SERIAL I/F

AND INTERRUPT

CONTROLLER

(RS–232–DVRS/RCVRS)

68901

BUS

ARBITRATION

DMA

HNDSHK

2MHZ

(23)

RD

WR

INTA

DMA HNDSHK

EPROM

160K x 16

NLOAD

NRST

N

NDAV

DSTBOUT

ERROR

DELETE CODE DETECT

OVERRUN DETECT

SERIAL AND

RR

4MHZ

4MHZ

2MHZ

(16)

DATA BUS

ADDRESS BUS

ADDRESS BUS

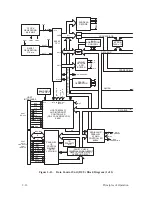

Figure 2–13. Data Control Unit (DCU) Block Diagram (1 of 2)

Summary of Contents for P9012

Page 1: ...P N 132305 001 Rev E P9012 Multifunction Line Printer...

Page 49: ...2 31 Principles of Operation Power Supply PCBAs 1 3 SHORT OPEN Figure 2 21 Power Supply PCBA...

Page 58: ...2 40 Principles of Operation...

Page 84: ...4 18 Troubleshooting...

Page 118: ...5 34 Alignments and Adjustments...

Page 203: ...6 85 Replacement Procedures This page intentionally left blank...

Page 214: ...6 96 Replacement Procedures...

Page 236: ...A 22 Power Paper Stacker Maintenance...

Page 246: ...D 2 Torque Table...

Page 254: ...Index 6...

Page 255: ......

Page 256: ...132305 001 Rev E...