544

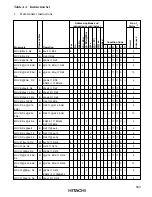

Condition Code

Mnemonic

Operation

I

H

N

Z

V

C

MOV.W @aa:24, Rd

W

@aa:24

→

Rd16

6

— —

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

0

—

8

MOV.W Rs, @ERd

W

Rs16

→

@ERd

2

— —

0

—

4

MOV.W Rs, @(d:16,

W

Rs16

→

@(d:16, ERd)

4

— —

0

—

6

ERd)

MOV.W Rs, @(d:24,

W

Rs16

→

@(d:24, ERd)

8

— —

0

—

8

ERd)

MOV.W Rs, @–ERd

W

ERd32–2

→

ERd32

2

— —

0

—

6

Rs16

→

@ERd

MOV.W Rs, @aa:16

W

Rs16

→

@aa:16

4

— —

0

—

6

MOV.W Rs, @aa:24

W

Rs16

→

@aa:24

6

— —

0

—

8

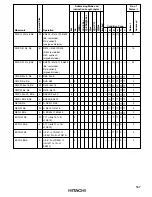

MOV.L #xx:32, Rd

L

#xx:32

→

Rd32

6

— —

0

—

6

MOV.L ERs, ERd

L

ERs32

→

ERd32

2

— —

0

—

2

MOV.L @ERs, ERd

L

@ERs

→

ERd32

4

— —

0

—

8

MOV.L @(d:16, ERs),

L

@(d:16, ERs)

→

ERd32

6

— —

0

—

10

ERd

MOV.L @(d:24, ERs),

L

@(d:24, ERs)

→

ERd32

10

— —

0

—

14

ERd

MOV.L @ERs+, ERd

L

@ERs

→

ERd32

4

— —

0

—

10

ERs32+4

→

ERs32

MOV.L @aa:16, ERd

L

@aa:16

→

ERd32

6

— —

0

—

10

MOV.L @aa:24, ERd

L

@aa:24

→

ERd32

8

— —

0

—

12

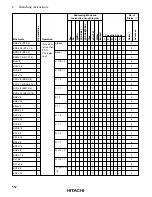

MOV.L ERs, @ERd

L

ERs32

→

@ERd

4

— —

0

—

8

MOV.L ERs, @(d:16,

L

ERs32

→

@(d:16, ERd)

6

— —

0

—

10

ERd)

MOV.L ERs, @(d:24,

L

ERs32

→

@(d:24, ERd)

10

— —

0

—

14

ERd)

MOV.L ERs, @–ERd

L

ERd32–4

→

ERd32

4

— —

0

—

10

ERs32

→

@ERd

MOV.L ERs, @aa:16

L

ERs32

→

@aa:16

6

— —

0

—

10

MOV.L ERs, @aa:24

L

ERs32

→

@aa:24

8

— —

0

—

12

POP.W Rn

W

@SP

→

Rn16

2

— —

0

—

6

SP+2

→

SP

POP.L ERn

L

@SP

→

ERn32

4

— —

0

—

10

SP+4

→

SP

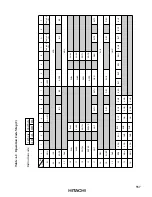

#xx

Rn

@ERn

@(d, ERn)

@–ERn/@ERn+

@aa

@(d, PC)

@@aa

Implied

Addressing Mode and

Instruction Length (bytes)

Normal

No. of

States

*

1

Advanced

Operand Size