77

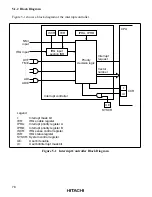

Section 5 Interrupt Controller

5.1 Overview

5.1.1 Features

The interrupt controller has the following features:

•

Interrupt priority registers (IPRs) for setting interrupt priorities

Interrupts other than NMI can be assigned to two priority levels on a module-by-module basis

in interrupt priority registers A and B (IPRA and IPRB).

•

Three-level masking by the I and UI bits in the CPU condition code register (CCR)

•

Independent vector addresses

All interrupts are independently vectored; the interrupt service routine does not have to identify

the interrupt source.

•

Five external interrupt pins

NMI has the highest priority and is always accepted; either the rising or falling edge can be

selected. For each of IRQ

0

, IRQ

1

, IRQ

4

, and IRQ

5

, sensing of the falling edge or level sensing

can be selected independently.