421

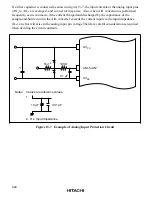

13.4.3 Input Sampling and A/D Conversion Time

The A/D converter has a built-in sample-and-hold circuit. The A/D converter samples the analog

input at a time t

D

after the ADST bit is set to 1, then starts conversion. Figure 13-5 shows the A/D

conversion timing. Table 13-4 indicates the A/D conversion time.

As indicated in figure 13-5, the A/D conversion time includes t

D

and the input sampling time. The

length of t

D

varies depending on the timing of the write access to ADCSR. The total conversion

time therefore varies within the ranges indicated in table 13-4.

In scan mode, the values given in table 13-4 apply to the first conversion. In the second and

subsequent conversions the conversion time is fixed at 256 states when CKS = 0 or 128 states

when CKS = 1.

(1)

(2)

ø

Address bus

Write signal

Input sampling

timing

ADF

t

D

t

SPL

t

CONV

Legend

(1):

(2):

t

D

:

t

SPL

:

t

CONV

:

ADCSR write cycle

ADCSR address

Synchronization delay

Input sampling time

A/D conversion time

Figure 13-5 A/D Conversion Timing