552

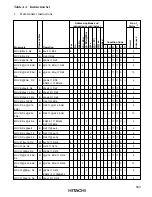

6.

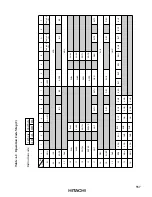

Branching instructions

Condition Code

Mnemonic

Operation

I

H

N

Z

V

C

BRA d:8 (BT d:8)

—

Always

2

— — — — — —

4

BRA d:16 (BT d:16)

—

4

— — — — — —

6

BRN d:8 (BF d:8)

—

Never

2

— — — — — —

4

BRN d:16 (BF d:16)

—

4

— — — — — —

6

BHI d:8

—

C

∨

Z = 0

2

— — — — — —

4

BHI d:16

—

4

— — — — — —

6

BLS d:8

—

C

∨

Z = 1

2

— — — — — —

4

BLS d:16

—

4

— — — — — —

6

BCC d:8 (BHS d:8)

—

C = 0

2

— — — — — —

4

BCC d:16 (BHS d:16)

—

4

— — — — — —

6

BCS d:8 (BLO d:8)

—

C = 1

2

— — — — — —

4

BCS d:16 (BLO d:16)

—

4

— — — — — —

6

BNE d:8

—

Z = 0

2

— — — — — —

4

BNE d:16

—

4

— — — — — —

6

BEQ d:8

—

Z = 1

2

— — — — — —

4

BEQ d:16

—

4

— — — — — —

6

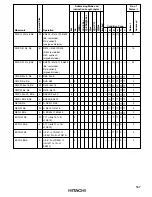

BVC d:8

—

V = 0

2

— — — — — —

4

BVC d:16

—

4

— — — — — —

6

BVS d:8

—

V = 1

2

— — — — — —

4

BVS d:16

—

4

— — — — — —

6

BPL d:8

—

N = 0

2

— — — — — —

4

BPL d:16

—

4

— — — — — —

6

BMI d:8

—

N = 1

2

— — — — — —

4

BMI d:16

—

4

— — — — — —

6

BGE d:8

—

N

⊕

V = 0

2

— — — — — —

4

BGE d:16

—

4

— — — — — —

6

BLT d:8

—

N

⊕

V = 1

2

— — — — — —

4

BLT d:16

—

4

— — — — — —

6

BGT d:8

—

2

— — — — — —

4

BGT d:16

—

4

— — — — — —

6

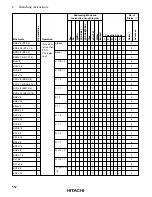

#xx

Rn

@ERn

@(d, ERn)

@–ERn/@ERn+

@aa

@(d, PC)

@@aa

Implied

Addressing Mode and

Instruction Length (bytes)

Normal

No. of

States

*

1

Advanced

Operand Size

Z

∨

(N

⊕

V)

= 0

If condition

is true then

PC

←

PC+d else

next;