290

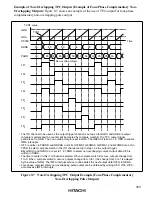

Different Triggers for TPC Output Groups 2 and 3: If TPC output groups 2 and 3 are triggered

by different compare match events, the address of the upper 4 bits of NDRB (group 3)* is H'FFA4

and the address of the lower 4 bits (group 2) is H'FFA6. Bits 3 to 0 of address H'FFA4 and bits 7

to 4 of address H'FFA6 are reserved bits that cannot be modified and always read 1.

Note:

* Since this LSI does not have a TP

14

pin, the TP

14

signal cannot be output off-chip.

Address H'FFA4

Bit

Initial value

Read/Write

7

NDR15

0

R/W

6

NDR14

0

R/W

5

NDR13

0

R/W

4

NDR12

0

R/W

3

—

1

—

2

—

1

—

1

—

1

—

0

—

1

—

Reserved bits

Next data 15 to 12

These bits store the next output

data for TPC output group 3

Address H'FFA6

Bit

Initial value

Read/Write

7

—

1

—

6

—

1

—

5

—

1

—

4

—

1

—

3

NDR11

0

R/W

2

NDR10

0

R/W

1

NDR9

0

R/W

0

NDR8

0

R/W

Next data 11 to 8

These bits store the next output

data for TPC output group 2

Reserved bits