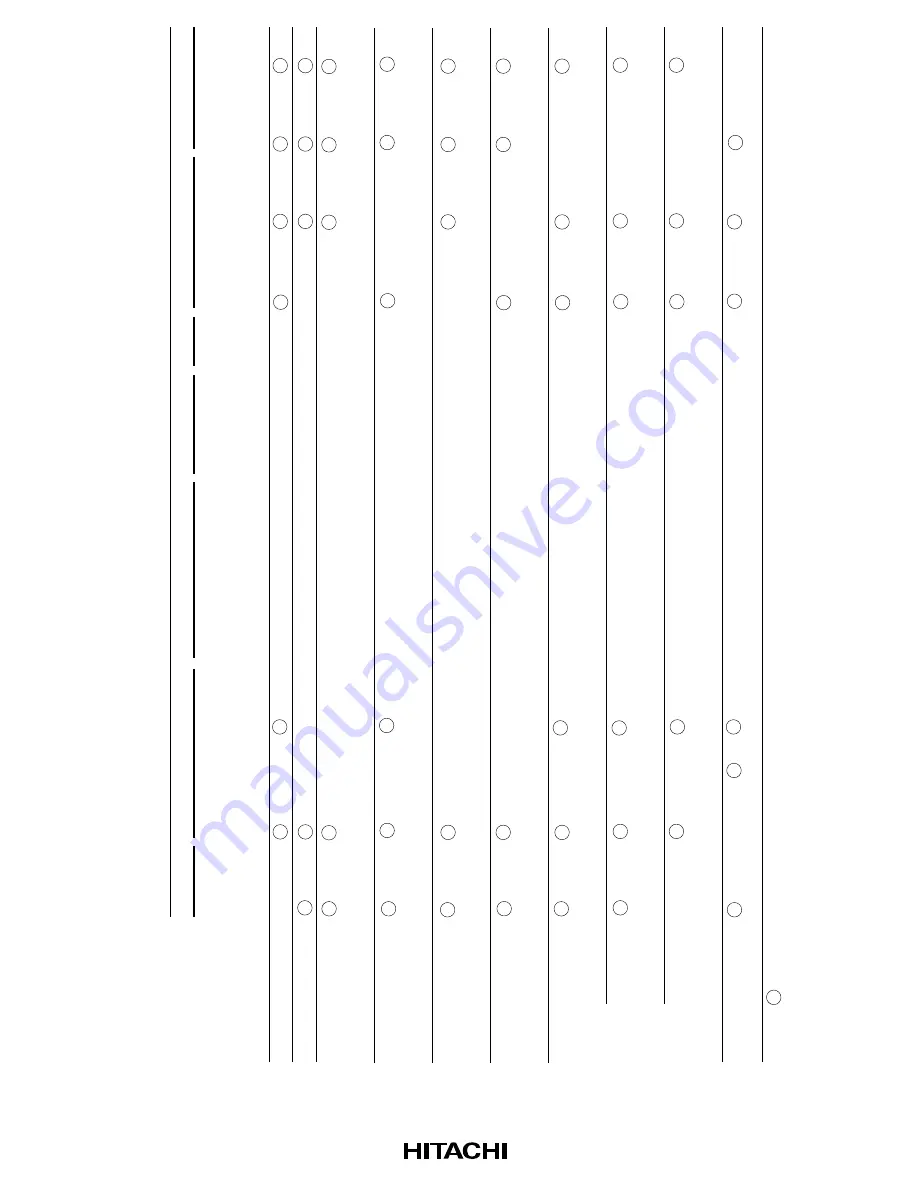

278

T

able 8-1

1 (c) ITU Operating Modes (Channel 2)

Register Settings

TSNC

TMDR

TFCR

T

OCR

T

OER

TIOR2

TCR2

Reset-

Comple-

Synchro-

Output

Synchro-

mentary nized

Buffer-

Level

Master

Clear

Clock

Operating Mode

nization

MDF

FDIR

PWM

PWM

PWM

ing

XTGD

Select

Enable

IOA

IOB

Select

Select

Synchronous preset

SYNC2 = 1

—

—

—

—

—

—

—

PWM mode

—

PWM2 = 1

—

—

—

—

—

—

—

*

Output compare A

—

PWM2 = 0

—

—

—

—

—

—

IOA2 = 0

Other bits

unrestricted

Output compare B

—

—

—

—

—

—

—

IOB2 = 0

Other bits

unrestricted

Input capture A

—

PWM2 = 0

—

—

—

—

—

—

IOA2 = 1

Other bits

unrestricted

Input capture B

—

PWM2 = 0

—

—

—

—

—

—

IOB2 = 1

Other bits

unrestricted

Counter

By compare

—

—

—

—

—

—

—

CCLR1 = 0

clearing

match/input

CCLR0 = 1

capture A

By compare

—

—

—

—

—

—

—

CCLR1 = 1

match/input

CCLR0 = 0

capture B

Syn-

SYNC2 = 1

—

—

—

—

—

—

—

CCLR1 = 1

chronous

CCLR0 = 1

clear

Phase counting

MDF = 1

—

—

—

—

—

—

—

mode

Legend:

Setting available (valid). — Setting does not affect this mode.

Note:

The input capture function cannot be used in PWM mode. If compare match A and compare match B occur simultaneously

, the

compare match signal is inhibited.