135

7.3 Port 2

7.3.1 Overview

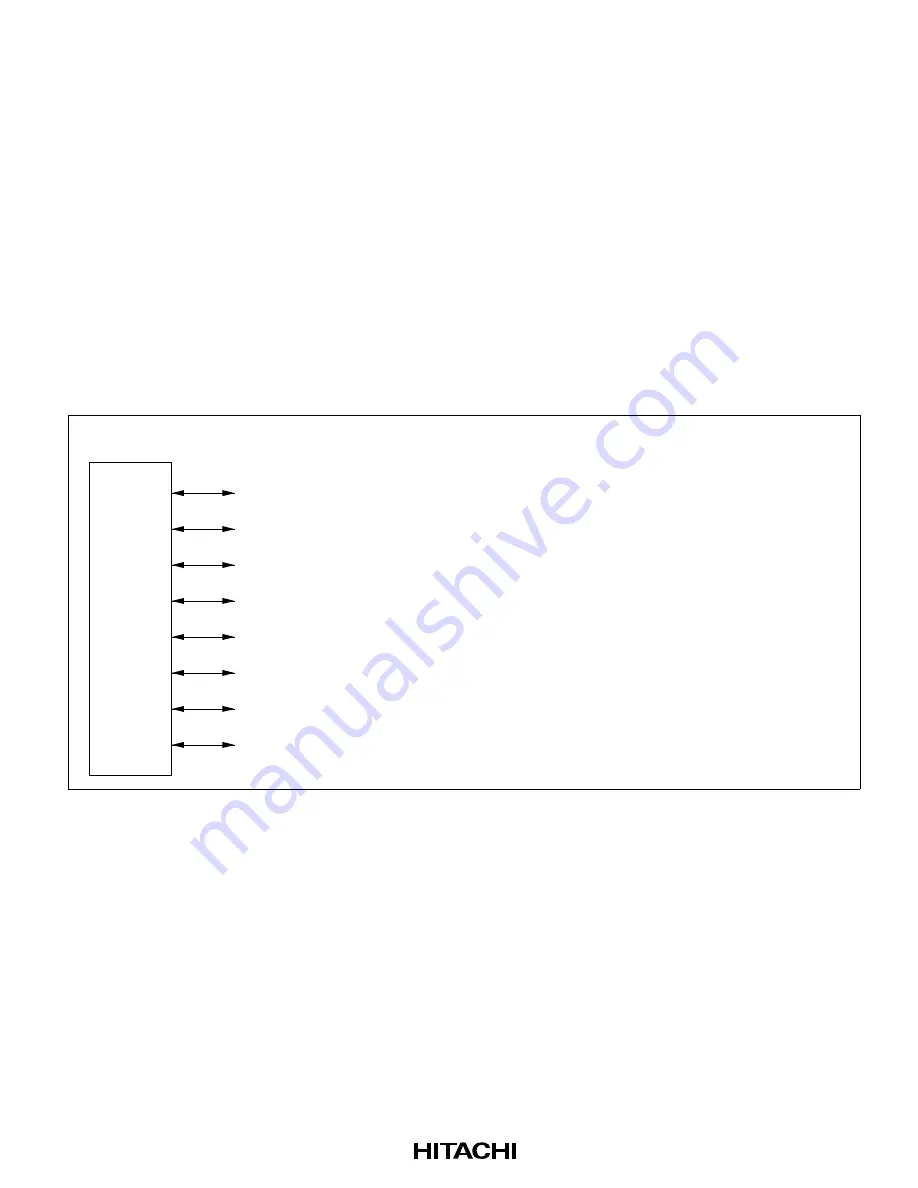

Port 2 is an 8-bit input/output port with the pin configuration shown in figure 7-5. Pin functions

differ according to operation mode.

In modes 1 and 3 (expanded mode with on-chip ROM disabled), port 2 consists of address bus

output pins (A

15

to A

8

). In modes 5 and 6 (expanded mode with on-chip ROM enabled), settings in

the port 2 data direction register (P2DDR) can designate pins for address bus output (A

15

to A

8

) or

generic input. In mode 7 (single-chip mode), port 2 is a generic input/output port.

Port 2 has software-programmable built-in pull-up transistors. Pins in port 2 can drive one TTL

load and a 90-pF capacitive load. They can also drive a Darlington transistor pair.

Port 2

P2 /A

P2 /A

P2 /A

P2 /A

P2 /A

P2 /A

P2 /A

P2 /A

7

6

5

4

3

2

1

0

15

14

13

12

11

10

9

8

P2 (input/output)

P2 (input/output)

P2 (input/output)

P2 (input/output)

P2 (input/output)

P2 (input/output)

P2 (input/output)

P2 (input/output)

7

6

5

4

3

2

1

0

A (output)

A (output)

A (output)

A (output)

A (output)

A (output)

A (output)

A (output)

15

14

13

12

11

10

9

8

Port 2 pins

Mode 7

Modes 1 and 3

P2 (input)/A (output)

P2 (input)/A (output)

P2 (input)/A (output)

P2 (input)/A (output)

P2 (input)/A (output)

P2 (input)/A (output)

P2 (input)/A (output)

P2 (input)/A (output)

7

6

5

4

3

2

1

0

Modes 5 and 6

15

14

13

12

11

10

9

8

Figure 7-5 Port 2 Pin Configuration