655

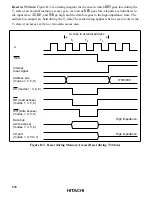

Pin Name

Mode

Reset State

Hardware

Standby

Mode

Software

Standby

Mode

Program

Execution State

Sleep Mode

P8

0

1, 3, 5, 6

T

T

keep

I/O port

7

T

T

keep

I/O port

P8

1

1, 3, 5, 6

T

T

[DDR = 0]

T

[DDR = 0]

Input port

[DDR = 1]

H

[DDR = 1]

H

7

T

T

keep

I/O port

P9

5

to P9

0

1, 3, 5 to 7

T

T

keep

I/O port

PA

3

to PA

0

1, 3, 5 to 7

T

T

keep

I/O port

PA

6

to PA

4

3, 6

T

T

[ADRCR = 0]

T

[ADRCR = 1]

keep

[ADRCR = 0]

A

21

to A

23

[ADRCR = 1]

I/O port

1, 5, 7

T

T

keep

I/O port

PA

7

3, 6

L

T

T

A

20

1, 5, 7

T

T

keep

I/O port

PB

7

, PB

5

to

PB

0

1, 3, 5 to 7

T

T

keep

I/O port

Legend

H:

High

L:

Low

T:

High-impedance state

keep: Input pins are in the high-impedance state; output pins maintain their previous state.

DDR: Data direction register

ADRCR: Address control register

Notes: 1. Masked ROM version. Dedicated FWE input pin for the F-ZTAT version.

2. Low output only when WDT overflows causes a reset.