113

6.3 Operation

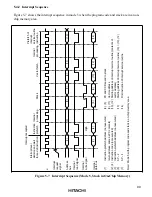

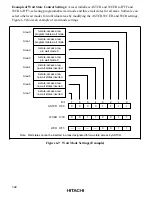

6.3.1 Area Division

The external address space is divided into areas 0 to 7. Each area has a size of 128 kbytes in the

1-Mbyte mode and 2 Mbytes in the 16-Mbyte mode. Figure 6-2 shows a general view of the

memory map.

Notes: There is no area division in mode 7.

1. The number of access states to on-chip ROM, on-chip RAM, and on-chip I/O registers is fixed.

2. This area follows area 7 specifications when the RAME bit in SYSCR is 0.

3. This area follows area 7 specifications.

H'00000

Area 0 (128 kbytes)

Area 1 (128 kbytes)

Area 2 (128 kbytes)

Area 3 (128 kbytes)

Area 4 (128 kbytes)

Area 5 (128 kbytes)

Area 6 (128 kbytes)

Area 7 (128 kbytes)

On-chip RAM

*

1,

*

2

a.

H'1FFFF

H'20000

H'3FFFF

H'40000

H'5FFFF

H'60000

H'7FFFF

H'80000

H'9FFFF

H'A0000

H'BFFFF

H'C0000

H'DFFFF

H'E0000

H'FFFFF

b.

H'000000

Area 0 (2 Mbytes)

Area 1 (2 Mbytes)

Area 2 (2 Mbytes)

Area 3 (2 Mbytes)

Area 4 (2 Mbytes)

Area 5 (2 Mbytes)

Area 6 (2 Mbytes)

Area 7 (2 Mbytes)

On-chip RAM

*

1,

*

2

H'1FFFFF

H'200000

H'3FFFFF

H'400000

H'5FFFFF

H'600000

H'7FFFFF

H'800000

H'9FFFFF

H'A00000

H'BFFFFF

H'C00000

H'DFFFFF

H'E00000

H'FFFFFF

H'00000

Area 1 (128 kbytes)

Area 2 (128 kbytes)

Area 3 (128 kbytes)

Area 4 (128 kbytes)

Area 5 (128 kbytes)

Area 6 (128 kbytes)

H'1FFFF

H'20000

H'3FFFF

H'40000

H'5FFFF

H'60000

H'7FFFF

H'80000

H'9FFFF

H'A0000

H'BFFFF

H'C0000

H'DFFFF

H'E0000

H'FFFFF

1-Mbyte modes with

on-chip ROM disabled

(mode 1)

16-Mbyte modes with

on-chip ROM disabled

(mode 3)

c. 1-Mbyte mode with

on-chip ROM enabled

(mode 5)

Area 7 (128 kbytes)

On-chip RAM

*

1,

*

2

On-chip ROM

*

1

Area 0 (128 kbytes)

H'000000

Area 1 (2 Mbytes)

Area 2 (2 Mbytes)

Area 3 (2 Mbytes)

Area 4 (2 Mbytes)

Area 5 (2 Mbytes)

Area 6 (2 Mbytes)

H'1FFFFF

H'200000

H'3FFFFF

H'400000

H'5FFFFF

H'600000

H'7FFFFF

H'800000

H'9FFFFF

H'A00000

H'BFFFFF

H'C00000

H'DFFFFF

H'E00000

H'FFFFFF

d. 16-Mbyte modes

(mode 6)

Area 7 (2 Mbytes)

On-chip RAM

*

1,

*

2

External

address space

*

3

On-chip

I/O registers

*

1

External

address space

*

3

On-chip

I/O registers

*

1

External

address space

*

3

On-chip

I/O registers

*

1

External

address space

*

3

On-chip

I/O registers

*

1

On-chip ROM

*

1

Area 0 (2 Mbytes)

Figure 6-2 Access Area Map (Mode 1, 3, and 5)