317

10.3 Operation

Operations when the WDT is used as a watchdog timer and as an interval timer are described

below.

10.3.1 Watchdog Timer Operation

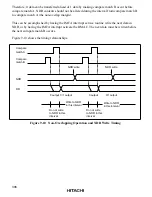

Figure 10-4 illustrates watchdog timer operation. To use the WDT as a watchdog timer, set the

WT/

IT

and TME bits to 1 in TCSR. Software must prevent TCNT overflow by rewriting the

TCNT value (normally by writing H'00) before overflow occurs. If TCNT fails to be rewritten and

overflows due to a system crash etc., the H8/3022 Series is internally reset for a duration of 518

states.

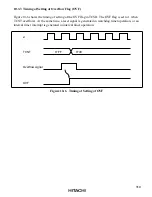

The watchdog reset signal can be externally output from the

RESO

pin* to reset external system

devices. The reset signal is output externally for 132 states. External output can be enabled or

disabled by the RSTOE bit in RSTCSR.

A watchdog reset has the same vector as a reset generated by input at the

RES

pin. Software can

distinguish a

RES

reset from a watchdog reset by checking the WRST bit in RSTCSR.

If a

RES

reset and a watchdog reset occur simultaneously, the

RES

reset takes priority.

Note: * Masked ROM version.

Since the

RES

pin is a dedicated FWE input pin with the F-ZTAT version, the reset signal

cannot be output to the outside.