260

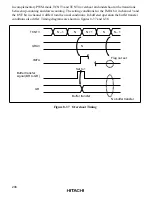

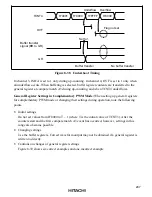

8.4.9 ITU Output Timing

The ITU outputs from channels 3 and 4 can be disabled by bit settings in TOER or by an external

trigger, or inverted by bit settings in TOCR.

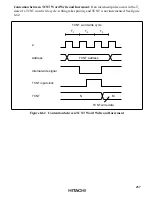

Timing of Enabling and Disabling of ITU Output by TOER: In this example an ITU output is

disabled by clearing a master enable bit to 0 in TOER. An arbitrary value can be output by

appropriate settings of the data register (DR) and data direction register (DDR) of the

corresponding input/output port. Figure 8-54 illustrates the timing of the enabling and disabling of

ITU output by TOER.

ø

Address

TOER

ITU output pin

TOER address

Timer output

I/O port

Generic input/output

ITU output

T

1

T

2

T

3

Figure 8-54 Timing of Disabling of ITU Output by Writing to TOER (Example)