197

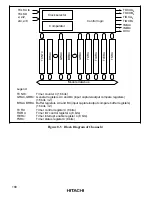

8.2.3 Timer Mode Register (TMDR)

TMDR is an 8-bit readable/writable register that selects PWM mode for channels 0 to 4. It also

selects phase counting mode and the overflow flag (OVF) setting conditions for channel 2.

Bit

Initial value

Read/Write

7

—

1

—

6

MDF

0

R/W

5

FDIR

0

R/W

4

PWM4

0

R/W

3

PWM3

0

R/W

0

PWM0

0

R/W

2

PWM2

0

R/W

1

PWM1

0

R/W

Reserved bit

PWM mode 4 to 0

These bits select PWM

mode for channels 4 to 0

Phase counting mode flag

Selects phase counting mode for channel 2

Flag direction

Selects the setting condition for the overflow

flag (OVF) in timer status register 2 (TSR2)

TMDR is initialized to H'80 by a reset and in standby mode.

Bit 7—Reserved: This bit cannot be modified and is always read as 1.

Bit 6—Phase Counting Mode Flag (MDF): Selects whether channel 2 operates normally or in

phase counting mode.

Bit 6

MDF

Description

0

Channel 2 operates normally

(Initial value)

1

Channel 2 operates in phase counting mode