Pro I: Analog Input Modules

Pro-AIn-8/16 Rev. C

ADwin

60

ADwin-Pro

Hardware, manual version 2.9, June 2006

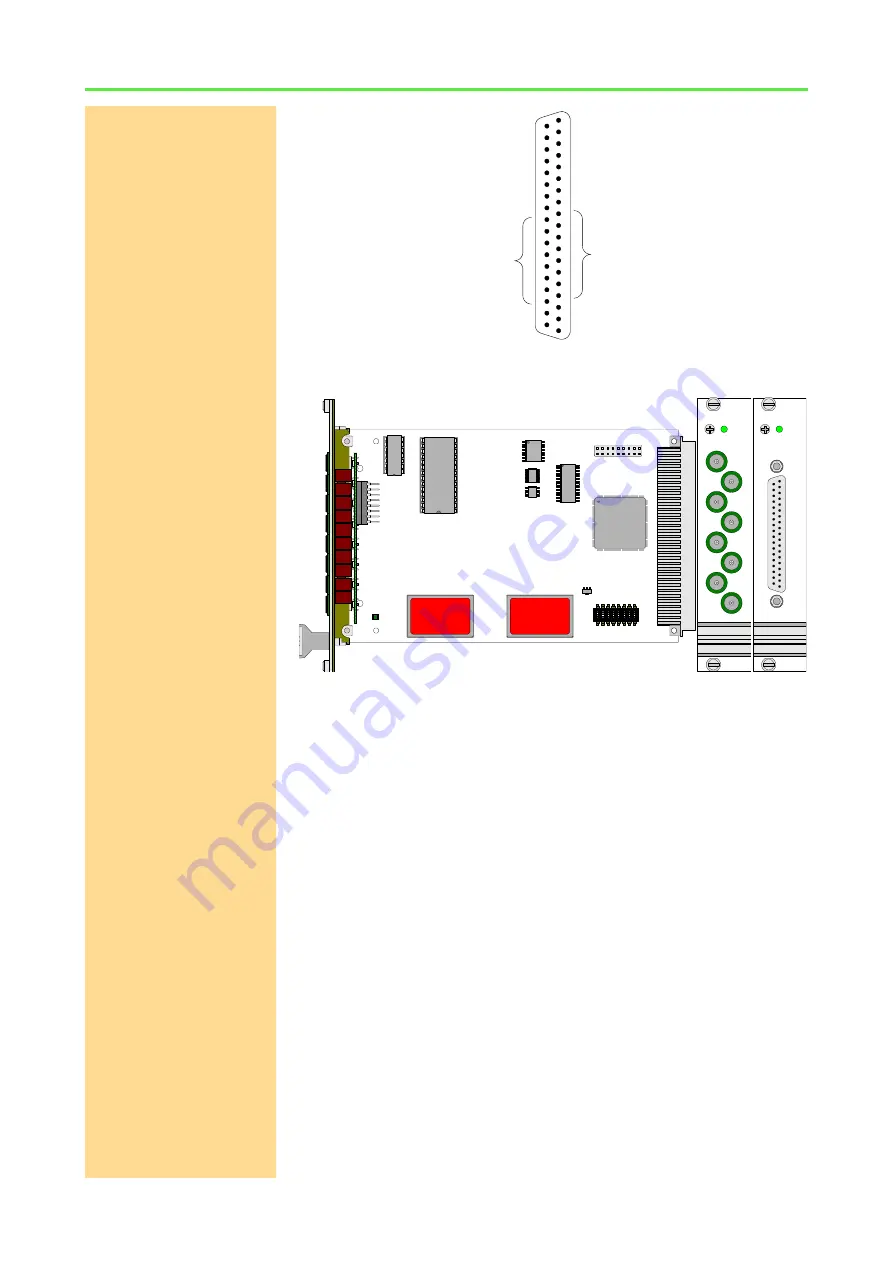

Fig. 101 – Pro-AIn-8/16-D Rev. C: Pin assignment differential

Fig. 102 –

: Board and front panel

ANALOG IN 1 (-)

ANALOG IN 2 (-)

ANALOG IN 3 (-)

ANALOG IN 4 (-)

ANALOG IN 5 (-)

ANALOG IN 6 (-)

ANALOG IN 7 (-)

ANALOG IN 8 (-)

AGND

RESERVED

ANALOG IN 1 (+)

ANALOG IN 2 (+)

ANALOG IN 3 (+)

ANALOG IN 4 (+)

ANALOG IN 5 (+)

ANALOG IN 6 (+)

ANALOG IN 7 (+)

ANALOG IN 8 (+)

AGND

RESERVED

DGND

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

RESERVED

RESERVED

19AD0102

A0 A1 A2 A3 A4 A5 A6 A7

74LS

19

ON

DIP

1

2

3

4

5

6

7

8

FPGA

A42MX16

D

G

407D

J

DC/DC CONVERTER

IN 5V OUT ±15V / ±65mA

DC/DC CONVERTER

IN 5V OUT ±5V / ±250mA

LT

C

1605C

S

W

MA

X

6225

D

S

1867

C

1-

100

P

G

A

206U

035

AIN8/16RB

ANALOG

INPUT

1

2

3

4

5

6

7

8

AIN8/16RB

ANALOG

INPUT