Chapter 23 Notes on Use of TMPR4937

23-4

In the case only one channel is used, restarting DMS transfer without a reset of FIFO results in a

malfunction when the conditions (1) to (3) are satisfied.

When two channels are used in a system, the following table shows settings to cause malfunctions.

Ch. A of a bus error

Ch. B

FIFO XFSZ Transfer FIFO XFSZ Transfer

Transfer restarted

in ch. A after a bus

error (without reset

of FIFO)

Ch. B after a bus

error

Disable

Any

value

Single Disable

Any

value

Single

Malfunction of ch. A

Malfunction of ch. B

Disable

Any

value

Single

Enable

<4DW

Single

Malfunction of ch. A

Malfunction of ch. B

Disable

Any

value

Single Enable

≥

4DW Burst

1)

Malfunction of ch. A

Correct operation of

ch. B

1)

1) By this setting, Channel B performs burst transfer. When the different off-set values are set to the

source address and destination address of Channel B, or source and destination burst inhibit bits

are set, single and burst transfer modes are combined for data transfer, but a malfunction does

not occur.

<Supplemental information> Dual address transfer mode

– Single transfer:

Disable FIFO (DMMCR.FIFUM[n]=0]

or the value smaller than 4DW is set to DMCCRn.XFSZ.

– Burst transfer:

Enable FIFO (DMMCR.FIFUM[n]=1]

and 4DW or larger value is set to DMCCRn.XFSZ.

[Workarounds]

Workarounds vary depending on which type of dual address transfer is performed together with dual

address single transfer. Combination of 4 channels in DMAC0 or DMAC1 affects a workaround to be

required.(DMAC0 and DMAC1 are independent controllers.)

Single Transfer

Burst Transfer

Workaround

(1)

1 ch.

Null

(a) or (b)

(2)

1 ch.

1 to 3 ch.

(b)

(3)

2 to 4 ch.

Null

(a)

(4)

2 to 3 ch.

1 to 2 ch.

(a)

(a)

Enable FIFO for all channels that perform single transfer.

(DMMCRn.FIFUM[n]=1: n=3 to 0)

(b) After all channels finished transfers, set 1 to RSFIF in DMMCRn, then write 0 to reset and

release reset of FIFO.

Содержание TX49 TMPR4937

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Страница 4: ......

Страница 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Страница 14: ...Table of Contents x ...

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4937 2005 3 Rev 2 0 ...

Страница 44: ......

Страница 52: ...Chapter 1 Overview and Features 1 6 ...

Страница 156: ...Chapter 7 External Bus Controller 7 56 ...

Страница 491: ...Chapter 16 Removed 16 1 16 Removed ...

Страница 492: ...Chapter 16 Removed 16 2 ...

Страница 493: ...Chapter 17 Removed 17 1 17 Removed ...

Страница 494: ...Chapter 17 Removed 17 2 ...

Страница 495: ...Chapter 18 Removed 18 1 18 Removed ...

Страница 496: ...Chapter 18 Removed 18 2 ...

Страница 497: ...Chapter 19 Removed 19 1 19 Removed ...

Страница 498: ...Chapter 19 Removed 19 2 ...

Страница 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

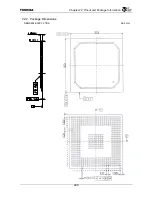

Страница 529: ...Chapter 22 Pinout and Package Information 22 9 22 2 Package Dimensions P BGA484 3535 1 27B9 Unit mm ...

Страница 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Страница 542: ...Chapter 24 Parts Number when Ordering 24 2 ...

Страница 544: ...Appendix A TX49 H3 Core Supplement A 2 ...