Chapter 7 External Bus Controller

7-16

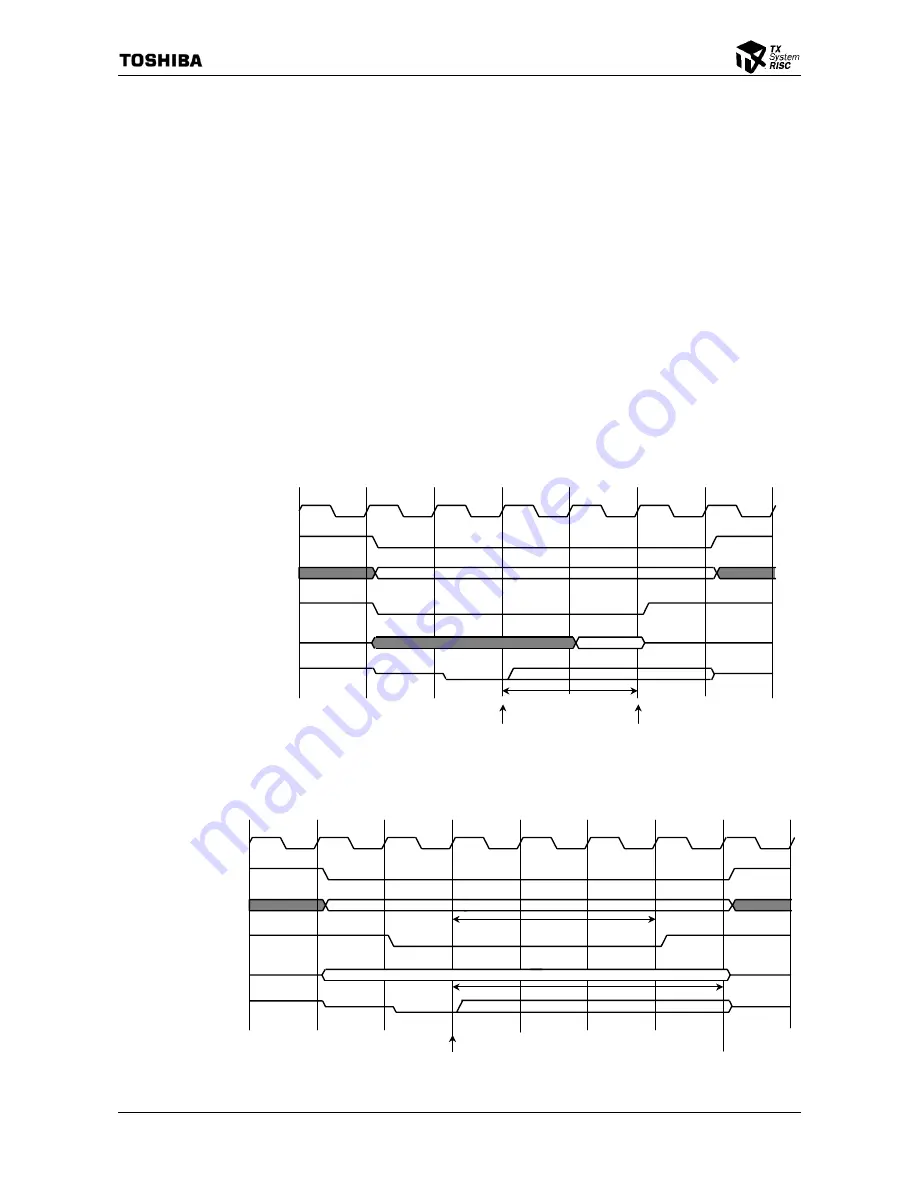

7.3.7.4 ACK

*

Input Timing (External ACK Mode)

The ACK* signal becomes an input signal when in the external ACK mode.

During a Read cycle, data is latched two clock cycles after assertion of the ACK* signal is

acknowledged (Figure 7.3.9 ACK* Input Timing (Single Read Cycle)). During a Write cycle,

assertion of the ACK* signal is acknowledged, SWE*/BWE* is deasserted three clock cycles

later, then data is held for one clock cycle after that (Figure 7.3.10 ACK* Input Timing (Single

Write Cycle).

The ACK* input signal is internally synchronized. Due to internal State Machine restrictions,

ACK* cannot be acknowledged consecutively on consecutive clock cycles. External devices can

assert ACK* across multiple clock cycles under the following conditions.

•

During Single access, the ACK* signal can be asserted before the end of the cycle during

which CE* is dasserted.

•

During Burst access, it is possible to assert the ACK* signal for up to three clock cycles

during Reads and for up to five clock cycles during Writes. If the ACK* signal is asserted for

a period longer than this, it will be acknowledged as the next valid ACK* signal.

Figure 7.3.9 ACK

*

Input Timing (Single Read Cycle)

Figure 7.3.10 ACK

*

Input Timing (Single Write Cycle)

SYSCLK

CE

*

ADDR [19

:

0]

OE

*

DATA [31

:

0]

ACK

*

/READY (Input)

Latch Data

Acknowledge ACK

*

2 clocks

EBCCRn.SHWT=0

SYSCLK

CE

*

ADDR [19:0]

SWE

*/

BWE

*

DATA [31:0]

ACK

*

/READY (Input)

3 clocks

4 clocks

Acknowledge ACK

*

EBCCRn.SHWT=0

Содержание TX49 TMPR4937

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Страница 4: ......

Страница 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Страница 14: ...Table of Contents x ...

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4937 2005 3 Rev 2 0 ...

Страница 44: ......

Страница 52: ...Chapter 1 Overview and Features 1 6 ...

Страница 156: ...Chapter 7 External Bus Controller 7 56 ...

Страница 491: ...Chapter 16 Removed 16 1 16 Removed ...

Страница 492: ...Chapter 16 Removed 16 2 ...

Страница 493: ...Chapter 17 Removed 17 1 17 Removed ...

Страница 494: ...Chapter 17 Removed 17 2 ...

Страница 495: ...Chapter 18 Removed 18 1 18 Removed ...

Страница 496: ...Chapter 18 Removed 18 2 ...

Страница 497: ...Chapter 19 Removed 19 1 19 Removed ...

Страница 498: ...Chapter 19 Removed 19 2 ...

Страница 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Страница 529: ...Chapter 22 Pinout and Package Information 22 9 22 2 Package Dimensions P BGA484 3535 1 27B9 Unit mm ...

Страница 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Страница 542: ...Chapter 24 Parts Number when Ordering 24 2 ...

Страница 544: ...Appendix A TX49 H3 Core Supplement A 2 ...