Chapter 9 SDRAM Controller

9-11

9.3.5

Low Power Consumption Function

9.3.5.1 Power Down Mode, Self-Refresh Mode

SDRAM has two low power consumption modes called the Power Down mode and the Self-

Refresh mode. Memory data is lost in the case of the Power Down mode since Memory Refresh is

not performed, but the amount of power consumed is reduced the most. Memory data is not lost in

the case of the Self-Refresh mode.

SDRAM is set to the Power Down mode by using the SDRAM Command Register (SDCCMD)

to issue the Power Down Mode command. Similarly, SDRAM is set to the Self-Refresh mode by

issuing the Self-Refresh Mode command. The SDRAMC terminates internal refresh circuit

operation after one of these commands has been issued. Issuing the Normal Mode command

returns operation to normal.

When the Power Down Auto Entry bit (SDCTR.PDAE) of the SDRAM Timing Register is set,

SDRAM is automatically set to the Power Down mode when memory access is not being

performed. The SDRAMC internal refresh circuit will continue operating, so there will be no loss

of memory data.

If either the Memory Access, Memory Refresh, or Memory command is executed while

SDRAM is set to the Power Down mode or the Self-Refresh mode, then the Power Down mode

and Self-Refresh mode will automatically terminate, and memory access will be performed.

After returning from a low power consumption mode that was set by either the Power Down

Mode command or the Self-Refresh Mode command, the next memory access starts after 10

SDCLK cycles pass. This latency sufficiently follows the stipulated time from Power Down to

first access of the SDRAM.

If setting the Power Down Auto Entry bit automatically causes memory access to be requested

when set in the Power Down mode, then add 1 SDCLK cycle more of access latency than when

not in the Power Down mode.

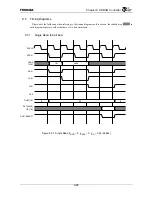

9.3.5.2 Advanced

CKE

Advanced CKE is a function that speeds up the CKE assertion and deassertion timing by 1

clock cycle. This function is set using the Address CKE bit (SDCTR.ACE) of the SDRAM Timing

Register.

Advanced CKE assumes that it will be used in a system where SDRAM data is saved even

when the power to the TX4937 itself is cut. Since CKE On/Off becomes 1 cycle faster, it is

possible to delay CKE by 1 clock cycle using external power consumption control logic. Please set

the SDRAM to the Self-Refresh mode before using this function.

When combining advanced CKE functionality with Power Down Auto Entry functionality and

memory access is requested while in the Power Down mode, two more SDCLK cycles of latency

are added than would be the case when not in the Power Down mode.

Содержание TX49 TMPR4937

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Страница 4: ......

Страница 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Страница 14: ...Table of Contents x ...

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4937 2005 3 Rev 2 0 ...

Страница 44: ......

Страница 52: ...Chapter 1 Overview and Features 1 6 ...

Страница 156: ...Chapter 7 External Bus Controller 7 56 ...

Страница 491: ...Chapter 16 Removed 16 1 16 Removed ...

Страница 492: ...Chapter 16 Removed 16 2 ...

Страница 493: ...Chapter 17 Removed 17 1 17 Removed ...

Страница 494: ...Chapter 17 Removed 17 2 ...

Страница 495: ...Chapter 18 Removed 18 1 18 Removed ...

Страница 496: ...Chapter 18 Removed 18 2 ...

Страница 497: ...Chapter 19 Removed 19 1 19 Removed ...

Страница 498: ...Chapter 19 Removed 19 2 ...

Страница 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Страница 529: ...Chapter 22 Pinout and Package Information 22 9 22 2 Package Dimensions P BGA484 3535 1 27B9 Unit mm ...

Страница 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Страница 542: ...Chapter 24 Parts Number when Ordering 24 2 ...

Страница 544: ...Appendix A TX49 H3 Core Supplement A 2 ...