Chapter 10 PCI Controller

10-21

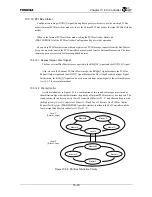

The Bus Master priority is determined based on the Level 1 round-robin sequence. However,

when Level 2 is used inside Level 1, the Level 2 Bus Master priority is determined based on the

Level 2 round-robin sequence.

All 8 Bus Masters cannot be used on the TX4937. However, the Bus Master priority would be

as follows if we assume there is a hypothetical device that can use all 8 Bus Masters and all 8 Bus

Masters (Masters A – D, W – Z) simultaneously requested the bus.

A

→

B

→

C

→

D

→

W

→

A

→

B

→

C

→

D

→

X

→

A

→

B

→

C

→

D

→

Y

→

A

→

B

→

C

→

D

→

Z

→

A (returns to the beginning)

Since the priority can only transition in the order indicated by the above arrows (or the arrows

in Figure 10.3.8, if we assume that the three Bus Masters A, B, and W exist, then Master B will

obtain the bus first. If A and W then simultaneously request the bus, then PCI Bus ownership will

transition in the order B

→

W

→

A.

10.3.12.3 Bus Parking

The On-chip PCI Bus Arbiter supports bus parking.

The last PCI Bus Master is made the Park Master when the Fix Park Master bit (FIXPM) of the

PCI Bus Arbiter Configuration Register (PBACFG) is cleared (in the default state). When this bit

is set, the Internal PCI Bus Arbiter Request A Port (Master A) becomes the Park Master.

10.3.12.4 Broken Master Detect

The TX4937 On-chip PCI Bus Arbiter has a function for automatically detecting broken

masters.

If the PCI Bus Master requests and is granted the bus when the PCI Bus is in the Idle state, this

master must assert the FRAME* signal within 16 PCI block cycles and start a transaction. The

PCI Bus Arbiter recognizes any device that breaks this rule as a broken bus master and removes

that device from the bus arbitration sequence.

This detection function is enabled when the Broken Master Check Enable bit (BMCEN) of the

PCI Bus Arbiter Configuration Register (PBACFG) is set. When a broken master is detected, the

Broken Master Detection bit (PBSTATUS.BMD) of the PCI Bus Arbiter Status Register is set and

the bit in the PCI Bus Arbiter Broken Master Register (PBABM) that corresponds to that master is

set. Then it also becomes possible to report an interrupt.

Содержание TX49 TMPR4937

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Страница 4: ......

Страница 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Страница 14: ...Table of Contents x ...

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4937 2005 3 Rev 2 0 ...

Страница 44: ......

Страница 52: ...Chapter 1 Overview and Features 1 6 ...

Страница 156: ...Chapter 7 External Bus Controller 7 56 ...

Страница 491: ...Chapter 16 Removed 16 1 16 Removed ...

Страница 492: ...Chapter 16 Removed 16 2 ...

Страница 493: ...Chapter 17 Removed 17 1 17 Removed ...

Страница 494: ...Chapter 17 Removed 17 2 ...

Страница 495: ...Chapter 18 Removed 18 1 18 Removed ...

Страница 496: ...Chapter 18 Removed 18 2 ...

Страница 497: ...Chapter 19 Removed 19 1 19 Removed ...

Страница 498: ...Chapter 19 Removed 19 2 ...

Страница 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Страница 529: ...Chapter 22 Pinout and Package Information 22 9 22 2 Package Dimensions P BGA484 3535 1 27B9 Unit mm ...

Страница 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Страница 542: ...Chapter 24 Parts Number when Ordering 24 2 ...

Страница 544: ...Appendix A TX49 H3 Core Supplement A 2 ...