Chapter 9 SDRAM Controller

9-1

9. SDRAM

Controller

9.1 Characteristics

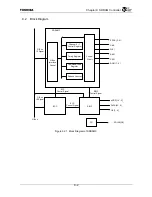

The SDRAM Controller (SDRAMC) generates the control signals required to interface with the SDRAM.

There are a total of four channels, which can each be operated independently. The SDRAM Controller

supports various bus configurations and a memory size of up to 2 GB.

The SDRAM has the following characteristics.

•

Memory clock (SDCLK) frequency: 50

−

133 MHz (For relationship between CPU clock and memory

clock, see Section 6.1)

•

Four independent memory channels

•

Can use registered DIMM

•

Selectable data bus width for each channel: 64-bit/32-bit

•

Supports critical word first access of the TX49/H3 core

•

Supports DMAC special Burst access (address decrement/fix)

•

Programmable SDRAM timing latency

Can set timing to match the clock frequency used and the memory speed. Can realize a system with

optimized memory performance.

•

Can write to any byte during Single or Burst Write operation. This feature is controlled by the DQM

signal.

•

Can set the refresh cycle to be programmable.

•

SDRAM refresh mode: both auto refresh and self refresh are possible.

•

Low power consumption mode: can select between self refresh or pre-charge power down

•

SDRAM Burst length: fixed to "2"

•

SDRAM addressing mode: Fixed to the Sequential mode

•

Supports systems with high fan-out

Supports two selectable data read-back buses and supports the Slow Write Burst Mode in order to

handle data buses with large load. In order to maintain timing consistency during Read operation, it is

possible to select whether to use the feedback clock to latch data or to by-pass this latch path. Two clock

cycles are used for each Write operation when in the Slow Write Burst Mode.

•

Can use the ECC or parity generation/check functions.

•

Can select EC (Error Check only), ECC (Error Check and Correct), or ECC + Scrub (write correction

data back to memory) when using the ECC function.

•

Can select Odd parity/Even parity when using the Parity function.

Содержание TX49 TMPR4937

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Страница 4: ......

Страница 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Страница 14: ...Table of Contents x ...

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4937 2005 3 Rev 2 0 ...

Страница 44: ......

Страница 52: ...Chapter 1 Overview and Features 1 6 ...

Страница 156: ...Chapter 7 External Bus Controller 7 56 ...

Страница 491: ...Chapter 16 Removed 16 1 16 Removed ...

Страница 492: ...Chapter 16 Removed 16 2 ...

Страница 493: ...Chapter 17 Removed 17 1 17 Removed ...

Страница 494: ...Chapter 17 Removed 17 2 ...

Страница 495: ...Chapter 18 Removed 18 1 18 Removed ...

Страница 496: ...Chapter 18 Removed 18 2 ...

Страница 497: ...Chapter 19 Removed 19 1 19 Removed ...

Страница 498: ...Chapter 19 Removed 19 2 ...

Страница 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Страница 529: ...Chapter 22 Pinout and Package Information 22 9 22 2 Package Dimensions P BGA484 3535 1 27B9 Unit mm ...

Страница 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Страница 542: ...Chapter 24 Parts Number when Ordering 24 2 ...

Страница 544: ...Appendix A TX49 H3 Core Supplement A 2 ...