Chapter 23 Notes on Use of TMPR4937

23-2

Bus errors occur the following three conditions.

(1) When CCFG.TOE of the Chip Configuration Register is set to “1” (Default: 0), G-Bus timeout

error detection is enabled, and the following situation results:

•

A Bus timeout occurs when a G-Bus Bus Master (TX49/H3 Core, DMAC, or PCIC) is reading

the G-Bus

•

A Bus timeout occurs when a G-Bus Bus Master (other than the TX49/H3 Core) is writing to

the G-Bus

(2) When ECCCR.MEB of the ECCCR Register in the SDRAM Controller is set to “1” (Default: 0),

Parity errors are enabled during a multi-bit error, and the following situation results:

•

A 2-bit ECC error or Parity error is detected during SDRAM Read operation by the TX49/H3

Core

•

A 2-bit ECC error or Parity error is detected during Read/Write operation by a G-Bus Bus

Master other than the TX49/H3 Core

(3) When PCICCFG.IRBER of the PCICCFG Register in the PCI Controller is set to “1” (Default: 1),

and the following situation results during initiator Read operation:

•

A Parity error is detected

•

A Master ABORT is received

•

A Target ABORT is received

•

A TRDY timeout is detected

•

A Retry timeout is detected

There is no problem for ColdReset or SoftReset exceptions because initialization processing is

performed after the exception occurs. Also, there is no problem for NMI exceptions if the process after

the exception occurs is similar to the above reset process.

[Workaround]

•

There is no problem if error notification to the TX49/H3 Core using Bus errors is not enabled

in the above Conditions.

•

Executing a SYNC instruction immediately after the preceding load instruction allows you to

avoid condition because the next instruction will not be executed until the Load data arrives.

Содержание TX49 TMPR4937

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Страница 4: ......

Страница 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Страница 14: ...Table of Contents x ...

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4937 2005 3 Rev 2 0 ...

Страница 44: ......

Страница 52: ...Chapter 1 Overview and Features 1 6 ...

Страница 156: ...Chapter 7 External Bus Controller 7 56 ...

Страница 491: ...Chapter 16 Removed 16 1 16 Removed ...

Страница 492: ...Chapter 16 Removed 16 2 ...

Страница 493: ...Chapter 17 Removed 17 1 17 Removed ...

Страница 494: ...Chapter 17 Removed 17 2 ...

Страница 495: ...Chapter 18 Removed 18 1 18 Removed ...

Страница 496: ...Chapter 18 Removed 18 2 ...

Страница 497: ...Chapter 19 Removed 19 1 19 Removed ...

Страница 498: ...Chapter 19 Removed 19 2 ...

Страница 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

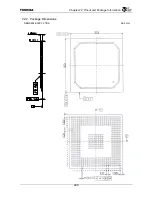

Страница 529: ...Chapter 22 Pinout and Package Information 22 9 22 2 Package Dimensions P BGA484 3535 1 27B9 Unit mm ...

Страница 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Страница 542: ...Chapter 24 Parts Number when Ordering 24 2 ...

Страница 544: ...Appendix A TX49 H3 Core Supplement A 2 ...