Chapter 10 PCI Controller

10-20

10.3.12 PCI Bus Arbiter

Configuration settings (DATA[2] signal) during boot up select whether to use the on-chip PCI Bus

arbiter (Internal PCI Bus Arbiter mode) or to use the External PCI Bus arbiter (External PCI Bus Arbiter

mode).

When in the Internal PCI Bus Abiter mode, setting the PCI Bus Arbiter Enable bit

(PBACFG.PBAEN) of the PCI Bus Arbiter Configuration Register starts operation.

The on-chip PCI Bus arbiter can arbitrate eight sets of PCI Bus usage requests from the Bus Master.

Five ports are used: one for the PCI Controller bus master and four for External Bus masters. The three

remaining ports are reserved for future expanded features.

10.3.12.1 Request Signal, Grant Signal

The four external Bus Masters are connected to the REQ[3:0] signal and the GNT[3:0]* signal.

Also, when in the External PCI Bus Master mode, the REQ[0]* signal becomes the PCI Bus

Request Output signal and the GNT[0]* signal becomes the Bus Usage Permission Input Signal.

Furthermore, the REQ[1]* signal can be used as an interrupt output signal to the external devices

(see 14.3.7 for more information).

10.3.12.2 Priority Control

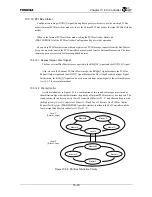

As illustrated below in Figure 10.3.8, a combination of two round-robin sequences is used as

the arbitration algorithm that determines the priority of Internal PCI Bus arbiter bus requests. The

round-robin with the lower priority (Level 2) consists of Masters W - Z, and the round-robin with

the high priority (Level 1), consists of Master A - D and Level 2 Masters. The PCI Bus Arbiter

Request Port Register (PBAREQPORT) specifies whether to allocate the PCI Controller and the

four External Bus Masters to Masters A-D or W - Z.

Figure 10.3.8 PCI Bus Arbitration Priority

Level 2

(Priority: Low)

Level 1

(Prirority: High)

Master A

Level 2

Master Z

Master X

Master W

Master B

Master C

Master D

Master Y

Содержание TX49 TMPR4937

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Страница 4: ......

Страница 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Страница 14: ...Table of Contents x ...

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4937 2005 3 Rev 2 0 ...

Страница 44: ......

Страница 52: ...Chapter 1 Overview and Features 1 6 ...

Страница 156: ...Chapter 7 External Bus Controller 7 56 ...

Страница 491: ...Chapter 16 Removed 16 1 16 Removed ...

Страница 492: ...Chapter 16 Removed 16 2 ...

Страница 493: ...Chapter 17 Removed 17 1 17 Removed ...

Страница 494: ...Chapter 17 Removed 17 2 ...

Страница 495: ...Chapter 18 Removed 18 1 18 Removed ...

Страница 496: ...Chapter 18 Removed 18 2 ...

Страница 497: ...Chapter 19 Removed 19 1 19 Removed ...

Страница 498: ...Chapter 19 Removed 19 2 ...

Страница 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Страница 529: ...Chapter 22 Pinout and Package Information 22 9 22 2 Package Dimensions P BGA484 3535 1 27B9 Unit mm ...

Страница 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Страница 542: ...Chapter 24 Parts Number when Ordering 24 2 ...

Страница 544: ...Appendix A TX49 H3 Core Supplement A 2 ...