Chapter 15 Interrupt Controller

15-5

In addition to the above, the TX49/H3 core has a TX49/H3 core internal timer interrupt and two

software interrupts, but these interrupts are directly reported to the TX49/H3 core independently of this

Interrupt Controller. Please refer to the “64-bit TX System RISC TX49/H2, TX49/H3, TX49/H4 Core

Architecture” for more information.

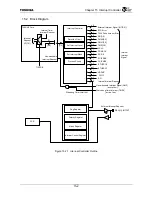

15.3.2 Interrupt request detection

In order to perform interrupt detection, each register of the Interrupt Controller is initialized, then the

IDE bit of the Interrupt Detection Enable Register (IRDEN) is set to “1.” All interrupts detected by the

Interrupt Controller are masked when this bit is cleared.

It is possible to set each interrupt factor detection mode using Interrupt Detection Mode Register 0

(IRDM0) and Interrupt Detection Mode Register 1 (IRDM1). There are four detection modes: Low

level, High level, falling edge, and rising edge.

The detected interrupt factors can be read out from the Interrupt Pending Register (IRPND).

15.3.3 Interrupt level assigning

Interrupt levels from 0 to 7 are assigned to each detected interrupt using the Interrupt Level Register

(IRLVL0-7). Interrupt level 7 is the highest priority and interrupt level1 is the lowest priority. Level 0

interrupts will be masked. (Table 15.3.2).

The priorities set by these interrupt levels will be given higher priority than the priorities provided

for each interrupt source indicated in Table 15.3.1.

Table 15.3.2 Interrupt Levels

Priority

Interrupt Level

(IRLVLn.ILm)

High 111

110

101

100

011

010

Low 001

Mask 000

Содержание TX49 TMPR4937

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Страница 4: ......

Страница 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Страница 14: ...Table of Contents x ...

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4937 2005 3 Rev 2 0 ...

Страница 44: ......

Страница 52: ...Chapter 1 Overview and Features 1 6 ...

Страница 156: ...Chapter 7 External Bus Controller 7 56 ...

Страница 491: ...Chapter 16 Removed 16 1 16 Removed ...

Страница 492: ...Chapter 16 Removed 16 2 ...

Страница 493: ...Chapter 17 Removed 17 1 17 Removed ...

Страница 494: ...Chapter 17 Removed 17 2 ...

Страница 495: ...Chapter 18 Removed 18 1 18 Removed ...

Страница 496: ...Chapter 18 Removed 18 2 ...

Страница 497: ...Chapter 19 Removed 19 1 19 Removed ...

Страница 498: ...Chapter 19 Removed 19 2 ...

Страница 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Страница 529: ...Chapter 22 Pinout and Package Information 22 9 22 2 Package Dimensions P BGA484 3535 1 27B9 Unit mm ...

Страница 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Страница 542: ...Chapter 24 Parts Number when Ordering 24 2 ...

Страница 544: ...Appendix A TX49 H3 Core Supplement A 2 ...